�뵼����ҵ����ȫ��ǰ���Կ�������ֵ����high-NA ��EUV����������һ�����ϵͳ����ػ�����ʩ��Ȼ��һ�������������

һ��ʱ��������ASML һֱ�ڿ��������ֵ�� (high-NA) EUV��̻�——������� 0.33 ��ֵ������ EUV ���ϵͳ�ĺ�����Ʒ��

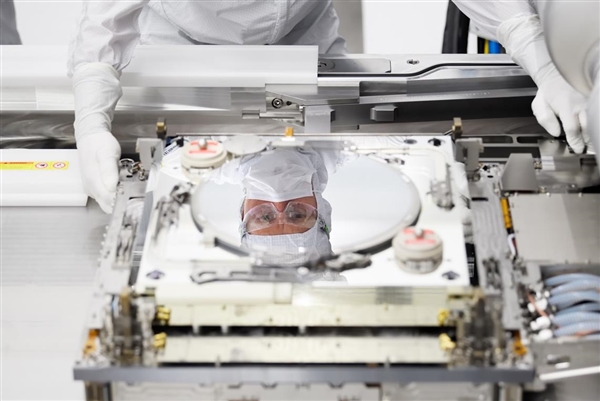

ASML �µĸ���ֵ�� EUV ϵͳ�漰һ��ȫ�µĹ��ߣ����� 0.55 ��ֵ���ľ�ͷ���ֱ���Ϊ 8 ���ף������й��ߵķֱ���Ϊ 13 ���ס�����ʦ��ʾ��0.55 NA ��EUV ���ߵ�Ŀ���� 2023 ��� 3nm����������Ϊ���豸��̫������ 2025 ��֮ǰͶ��������

�� KeyBanc �ƣ�һ̨High NA ��̻��ijɱ�Ԥ��Ϊ 3.186 ����Ԫ��������� EUV ϵͳ��Ϊ 1.534 ����Ԫ������ʵ�ϣ����ϵͳ���ܳɱ����ܻ���ߣ���Ϊ������Ҫ�������豸���¹���ģ�Ͳ�ͬ�Ĺ�̽���ʵ�ָ���ֵ�� EUV�����ֹ�Ӧ�̶����о���Щ������������һ������Ȼ����һЩ��ࡣ

����豸���ڶ�оƬ�ϵ�С��������ͼ������ʹоƬ�������ܹ��ڸ��ڵ��Ͽ�����С��������豸�����������������װ������оƬ���װ�С�

ֱ�� 2018 �꣬оƬ�����̶�ʹ�ô�ͳ�Ĺ�ѧ���ɨ������ǰ��оƬ�϶���������ͼ�����������Ƚ��Ľڵ��ϣ���̵�ͼ�������̱�ù��ڸ��ӣ���ʹ����˶� EUV�������ԶԶ������

ASMLʹ��13.5nm ������ 0.33 NA EUV ��̻��������Ǻ�̨������������ 7nm �� 5nm оƬ��Ӣ�ض�ҲΪ�Ƚ���оƬ���������� ASML �� EUV �豸�����Ǻ� SK ����ʿ����ʹ�� EUV ���� DRAM ������

оƬ�����̽�����ʹ�ý���� EUV������ijЩʱ��——������ 3nm �ڵ�֮���ij���ڵ㣬ʹ�����е� EUV ��δ����оƬ����ͼ��������ø�Ϊ���ѡ������High NA �豸�ʺϵĵط���

���ȣ�Ӣ�ض���Ϊ�ü���������Ҫ���������ƻ���װ ASML �ĵ�һ̨ 0.55 High NA EUV ��̻���

Ӣ�ض������ܲü漼���������ܾ��� Ann Kelleher ��ʾ��“�⽫����������ѧϰ����Ҳ��ʹ�����ܹ���������С�ļ��νṹ��չ��”

���Ǻ�̨����Ҳ���������ֵ�����ߡ�������High NA EUV�Ĺ����漰�����µĺ��ƶ��IJ�����“High NA������ 0.33 NA EUV �Ĵ���֪ʶ��”Cowen �ķ���ʦ Krish Sankar ˵��“EUV ������Թ�̽���˵������ս�ԡ���High NA ��Ǩ��Ҳ���߽����ԣ���̽������ܽ�������ߣ�������δ���ڵ�ij���Ҫ����ֵ���Ĺ�ѧԪ�����µģ���������Ȼ�Ƿ����ѧԪ����”

Ϊʲô��High NA��

�ھ�Բ���У�оƬ���������ù�̺������豸������оƬ��ʹ������ƽ����ɵ��ļ���ʽ������ģ�豸����һ����ģ����Ĥ�Ǹ���оƬ��Ƶ���ģ�壬���ձ����͵���Բ�����������Ƭ�����뵽Ϳ����/��Ӱ��ϵͳ�С���ϵͳ��һ�ֳ�Ϊ��̽��Ĺ������ϵ��ڹ�Ƭ�ϡ�

Ȼ����ģ��Ƭ������ɨ�����С��ڲ����У�ɨ���Dz����⣬�ù�ͨ��ϵͳ�е�һ��ͶӰ��ѧ��������ģ���䡣����й�̽����ڹ�Ƭ���γ�ͼ����

��������оƬ������ʹ�û���193nm �����Ĺ�̹�����ͼ������оƬ���ܡ�ͨ�����ּ�����оƬ�����̽� 193 ����̼�����չ�� 7 ���ס������� 5nm ʱ��ʹ����Щ����̫�����ˡ�

“��ӡ 50nm��40nm �� 30nm �������� 193nm �����˵��һ����еļ������” D2S��ϯִ�й� Aki Fujimura ˵��“�� 13.5 ���ײ�����ʹ�� EUV Ӧ�û�����ס������С�”

2018 �꣬���Ǻ�̨���������� ASML �� 0.33 NA EUV ɨ���ǣ��������� 7nm оƬ������� 5nm��ASML �� EUV ɨ����֧�� 13 ���ֱ��ʣ�������ΪÿСʱ 135 �� 145 ����Բ (wph)��

�� EUV �����������ù�����ʱ�ᵼ�²���Ҫ�ı仯��ȱ�ݡ�ϵͳ��������ʱ��Ҳ��һ�����⡣

������ˣ��� 7 ���ף�оƬ����������ʹ�� EUV ��ͼ����оƬ���������� 40 ����ʼ����Ӧ������ʹ�û��� EUV �ĵ�һͼ��������������뷨�ǽ�оƬ��������һ����ģ�ϣ�Ȼ��ʹ�õ��ι���ع⽫���Ǵ�ӡ�ھ�Բ�ϡ�

оƬ������ϣ����������չ EUV ��һͼ����EUV ���ι�ͼ�� 32nm �� 30nm ���ﵽ���ޣ����� 5nm �ڵ����ҡ�

����Щ��༰���ϣ������� 3nm �ڵ㣬оƬ��������ҪѰ���µ�ѡ�� EUV ˫ͼ������˫��ͼ�����У�����оƬ�����ָ���������ģ�ϲ������Ǵ�ӡ�ھ�Բ�ϡ���ȸ����ְ�����Ҳ�Ǿ�Բ��ͨ�� 193nm ��̼������յĶ�����

��Щ�˿���ϣ����ȫ���� EUV ˫��ͼ����“�����������ڽӽ� 0.33 NA EUV �����ع�ļ��ޣ�Ϊ���������ڿ���High NA EUV��”����TEL�Ĺ��չ���ʦ Arnaud Dauendorffer������� SPIE ����ģ���� + EUV �����ϵ��ݽ���˵��

Ϊ�˱��� EUV ˫��ͼ������оƬ�����������ƶ� 3nm �����ϵĸ���ֵ�� EUV��High-NA EUV ����ʵ�ָ��ĵ�ͼ��������

“�ù����ṩ�˸��ߵķֱ��ʡ�����ζ��������ʹ������ӡ����ܡ�����ͼ��Աȶȿ�ʵ�ָ��õľֲ� CD �����ԣ�”ASML ϵͳ�����ܼ� Jan van Schoot �ڻ����ϵ��ݽ���˵��

ASML �ĵ�һ������ֵ�� EUV ϵͳ EXE:5000������ 8nm �ֱ��ʺ� 150 wph �����������ͻ�����ʱ�䶨�� 2023 �ꡣȻ���� 2024 ��ף�ASML �������°汾 EXE:5200����������Ϊ 220 wph��

High-NA EUV �Ĺ���ԭ�������ڵ���� EUV ��̣�������һЩ�ؼ����졣�봫ͳ��ͷ��ͬ������ֵ�����߰���һ�����ξ�ͷ��֧��һ������Ŵ� 8 ������һ������Ŵ� 4 ���������ֶδ�С������һ�롣��ijЩ����£�оƬ�����̻���������ģ�ϼӹ�һ��оƬ��Ȼ����ģ�����һ��ӡˢ�ھ�Բ�ϣ�����һ�����ӵĹ��̡�

����ģ

High-NA EUV ����Ҫ�µĹ���ģ���͡�EUV �ʹ�ͳ�Ĺ�ѧ��ģ�Dz�ͬ�ġ���ѧ��ģ�ɲ��������ϵIJ���������ɣ���ʹ�����ǿ����⡣

�ж������͵Ĺ�ѧ��ģ�������Ԫ��ģ��������ģ (PSM)��

�ڶ�Ԫ��ģ�У�����ѡ����λ�ñ�ʴ�̣��Ӷ���¶���������塣�������������ط�û��ʴ�̡��ڲ����У��������䵽��ģ�ϲ��������в��������Ӷ���¶����Ƭ���ⲻ�ᴩ���Ƹ�����

����Ҳʹ�� PSM��“PSM �кܶ��֣������ǵĹ���ԭ����ʹ����λ����������Ҫ�Ĺ⣬�Ӷ������Աȶȸ��ߵ�ͼ��”Fractilia �� CTO Chris Mack ˵��

����� EUV ��ģ�Ƕ�Ԫ�ͷ���ġ�EUV ��ģ��/�������� 40 �� 50 �����⽻�污����ɣ�λ�ڻ����ϡ�������� 250 ���� 350 ����Ķ��ѵ����ڶ�ջ�ϣ���һ�������ɵĸ��Dz㣬Ȼ����һ����������ϵ���������

����ģ�����У���һ���Ǵ����������ģ��������ģ���Ϲ�Ӧ�����죬����������ģ�Ļ����ṹ��

Ϊ������ EUV ��ģ���ϣ���Ӧ�̽�����Ĺ���������������ϡ�ʹ�ù⻯��ѧ����豸�����ģ���ϵ�ȱ�ݡ�

Lasertec �������� EUV ��ģ���ϵĹ⻯���ϼ�� (ABI) ϵͳ��ABI ����ʹ�� 13.5 ���ײ��������� 1 ���ף��߶ȣ�x 40 ���ף����ȣ��������ȣ�ȱ�ݶ�λ����Ϊ 20 ���ס�

�������ֵ�� EUV��Lasertec ���ڿ���һ�־��� 1nm x 30nm �����ȵ��� ABI ϵͳ��“���ǵ�Ŀ���� 10nm ��ȱ��λ�ã�”Lasertec USA �ܲ� Masashi Sunako �ڻ����ϵ��ݽ���˵��

����Ҫ���ǣ�����ҵ���ڿ������� 3nm �����ϵ��� EUV ��ģ���͡��ڽ���� EUV ��Ĥ�У���������һ������ 3D ��������ͻ�������ֶ������ڲ����У�EUV ���� 6° �ĽǶ�������ģ��������ܻ��ڹ�Ƭ��������ӰЧӦ�����ģ����ij������������Ϊ���� 3D Ч�����ᵼ�²���Ҫ��ͼ������ƫ�ơ�

Ϊ�˼�����ЩӰ�죬EUV ��ģ��Ҫ���������ռ��������е� EUV ��ģ�У������ռ��ĺ��Ϊ 60 ���ס����������ø�������������50nm���Ⲣ���ܽ����ĤЧӦ����Ϊ��Ӧ��ҵ�����ڿ��������µ� EUV ��ģ���ͣ����� 2D���������塢�� k���Ƿ���� PSM��

EUV PSM �ƺ��������Ķ������ü������������ 3D Ч����ͬʱ��ͨ�����õĶԱȶ������ͼ��������

���� EUV PSM ������Ҫ��ͬ�IJ��ϡ�

�� SPIE Photomask/EUV �����ϵ��ݽ��У�������ѧ���о���Ա������һ������ EUV ��ģ�����ɻ����ϵ��ɺ轻�����ɡ��ɸ��Dz�λ�ڶ��ṹ�Ķ�����Ȼ������-��ʴ��ֹͣ�㣬�Լ���Ϊ���Ʋ��ϵ��ɺϽ�

��һƪ�����У�Hoya �����˸���˥���������������������������ܡ�“PSM ���������������棬”���� Hoya �� Ikuya Fukasawa ��һ���ݽ���˵��“��Ϊ�˿��� EUV PSM ���ϣ����DZ�������ܶ�Ҫ�����ղ��ϱ������С�ĴֲڶȺߵĿ���ģ�����;��ԡ���Ȼ���������������ģ������ʴ�̡�”

�� EUV PSM һ����High k ��ģҲ���з��С�High k EUV ��Ĥ�����ڽ���� EUV ��Ĥ������ҵ����̽�������������ϣ����������������������������ռ����Լ�����ģЧӦ�������ֲ��Ϻ���ʹ�á�

���ͬʱ��������˾ Astrileux ���������һ��ʹ���ɲ��ϵ����ͷǷ��� EUV ��ģ��Astrileux ��ϯִ�й� Supriya Jaiswal ��ʾ��“���ǵ���Ĥ�ںڰ��������������������������������屳��������й©���١�”

Astrileux ��������һ�� 2D ��Ĥ����������������������С���ҳ�����˾��̸������������Ĥ��������Щ�����з��С�

��Ŀǰ���ԣ�оƬ�����̽����������е� EUV ��ģ/�հṹ�������е� 0.33 NA EUV ���ߡ�Ȼ����ij��ʱ��оƬ�����̿��ܻ�Ϊ 0.33 EUV ���� EUV PSM��������ֵ�� EUV ������ʱ��оƬ�����̿��ܻ�ʹ�� PSM��High k ��������Ĥ����Ҳ�ǿ��ܵġ�

Hoya Group �� Hoya LSI �ܲ� Geoff Akiki ˵��“�������ķ�չ���м��ַ��������������ơ��� n ���Ǹ� k��” “���������ľ��Ͻ��Ǽ��ɲ�ʹ���������з������ã�������Ϊ��Ʒ�Ƴ������磬������ƽ̹�����������飬���ǻ��˺ܶ�ʱ�䵣�ġ�����ȱ�ݣ����Ƕ���̸�ۡ���ij��������˵��������Щ������ѡ�������ͼ����һ���Ƴ̴��ڡ������������ջ�ÿ��õĶ�����ԭ�����������������¡�”

�µ���Ĥ�豸

ͬʱ����Ĥ��һ���Ƴɣ��ͻᱻ��������Ĥ��Ӧ�̡�����ģ��Ӧ�̴�����blank����ͼ������ʴ�̡����ͼ�顣�����Ĥ��װ����Ĥ�ϡ�

���ȣ�����ģ������ʹ�ó�Ϊ��������ģд������ϵͳ���ݸ����� IC �������ģ��д��ͼ��������������ģ�������������ڿɱ���״���� (VSB) �����ĵ��������������ߡ��ڲ����У�����ģ����ϵͳ�У��������������ʽײ����ģ��

���� VSB ����ģ��д�������ڴ�ͳ�Ĺ�ѧ��ģ������ EUV ��ģ���и�С�����ӵ����������� VSB ̫�������������ͼ������

���� EUV ��һЩ���ӵĹ�ѧ��ģ����ģ������ʹ�ö������ģд������IMS Nanofabrication �Ķ������ģд�빤������ 262,000 ��С�������Ӷ��ӿ��˹��̡�д��ʱ���Ǻ㶨�ģ���Ҫ 12 ��Сʱ�������������������ͼ������

IMS �����Ƴ���ڶ������ߣ����а���һ���µ��з��汾��“���ڸ���ֵ�� EUV ��ģ���죬�µ� MBMW-301 ���߽��䱸���������”IMS ������ Hans Loeschner ˵��

NuFlare ���ڿ����������ģд��������Щϵͳּ�ڶ���һ�� EUV ��������ģ����ͼ����������ҵ����ʹ�÷����̼���(ILT)�ڸ�����ģ�Ͽ���������״����ν�� ILT ��Ĥ���� EUV�������Ǹ� NA ����ú���Ҫ��

“ILT ��ģ��һ����ǿ���մ��ڵķ���������߾�Բ�������ն�����仯�ĵ��ԣ�”D2S �� Fujimura ˵��

��ͼ��������֮����ģ�ṹ��ʴ�̺���࣬�γɹ���ģ�������������У�ȱ�ݿ��ܻ�����ڹ���ģ�ϡ�

����������⡣��Ϊ�ڹ�̹����У�����ɨ���ǵĹ������ģ���������ͼ��ͶӰ����Ƭ�ϡ������ģ��ȱ�ݣ���������ܻ�ӡ�ھ�Բ�ϡ����Ӱ����Ƭ�����ʣ�������ٵ�һ��оƬ��

��������ģ���������У����������ģ�Ƿ����ȱ�ݡ����ڴ�ͳ�Ĺ�ѧ��ģ������ģ������ʹ�ù�ѧ��ģ���ϵͳ��Applied Materials��KLA��Lasertec �� NuFlare ������Щϵͳ��

��ѧ�������Լ�� EUV ��ģ����ѧ�������Ƿֱ��ʡ����ǿ��ܻ��� 20 ���� 16 ���İ���ֱ�����ʧȥ������

��Ϊ��Ӧ��Lasertec ����Ƴ���һ��ʹ�� 13.5 ����Դ�Ĺ⻯ͼ����ģ��� (APMI) ϵͳ����С�IJ���ʹϵͳ�ܹ���λ EUV ��ģ���� 20 ����ȱ�ݡ�

Lasertec ���ڿ������ڸ���ֵ�� EUV ��ģ�� APMI ϵͳ��“�µĹ�ѧ������̽������ϵͳ����Ѿ���ɣ�”Lasertec �� Sunako ˵���ù��ƻ��� 2023/2024 ���Ƴ���

���˹�ѧ�� APMI���ͻ�������һ�� EUV ��ģ���ѡ��Ǿ���KLA �� NuFlare ���ڿ����������������ģ���ߡ�

NuFlare ���ڿ���һ�־��� 100 �������Ķ�������ϵͳ���ƻ��� 2023 ���Ƴ���“������Ϊ 15 ���ס����ʱ��Ϊÿ����Ĥ������� 6 Сʱ��”NuFlare ��ɼɭ����˵��

�ܶ���֮�����ڵ�ǰ��δ���� EUV ��ģ������ģ�����̽�ʹ�����м������——�⻯����������ѧ��

�ͼ��һ������Ĥ��Ҳ�ܹؼ��������ģ��ȱ�ݣ�����ģ�����̿���ʹ����ģ��ϵͳ�����ǡ���ģ���������������ͣ������������ӹ��������ǻ����ġ�

���ڸ��ڵ㣬��˾�Ƴ���һ��ʹ�õ���������������ģ�����ߡ���ϵͳ������Ĥ�� 10 ������С�ߴ缷ѹ���ϰ������ 60 ����ȱ�ݡ�

ͬʱ����³���ṩʹ�����ӹ���������ģ�����ߡ���Щϵͳ����һ��С�ļ��������ģȱ�ݡ�

������ģ�����߶���������Ƚ��ڵ����С������ȱ�ݳߴ硣���ǻ����봦�����ֲ��ϡ�“��Щ���յIJ��϶����Զ���ȥ�������������������ȱ����Ⱦ������Ҫ����Ϊ��������ͨ����δ֪�ģ�”��³�˼����ܼ�ܷ�·�տ����� (Jeff LeClaire) ˵��

��Ҫ�¹�̽�

��̽����ڹ��Ҳ����Ҫ��оƬ��������Ҫ�������÷ֱ��� [R]�����߿��ֲڶ� [L] �������� [S] �Ĺ�̽���

����ҵ�Ѿ����������ڹ�̵Ĺ�̽��������� EUV ��˵������Ͳ�ͬ�ˡ�����Ҫ�����ͬʱ������������������Ǻ����ѵģ���Ϊ������������ģ�����һ�������ĸĽ�ͨ�����ٻή�����������е�һ��——ͨ������Ϊ RLS Ȩ���ϵ��

���������� EUV ��̽��������ּ���——��ѧ�Ŵ�ʴ�� (CAR) �ͽ�����������ڹ�ѧ�� EUV �� CAR �漰һ�����ӵĹ��̡�������ײ��ɨ�����еĹ�̽�ʱ��������������Ӧ��

“��Ӧ������һ�����漰��ʼ���ӵĻ�ѧ�Ŵ����й�������ת��Ϊ�������ӣ�ÿ������������ջ��������������ӡ�CAR���������ڿ���ͨ������ÿ�����Ӳ����Ĺ�����ӵ���������߹�̽��������ȡ�Ȼ������Щ������ὫԽ��ԽԶ��ԭʼ���ӵ�λ�ã�����ͼ��ģ�����Ӷ����ͷֱ��ʲ������߱�Ե�ֲڶȡ�

�����������̽���̫���죬�����Ǿ���һЩ���ơ����磬Inpria �Ľ����������̽������������ṹ�����Ը���Ч�ز��� EUV ���ӡ�

���죬ҵ������Ѱ��һ���������ֵ�� EUV �� RLS Ҫ��Ĺ�̽�������Ȼ��һ�����ڽ��еĹ�����Paul Scherrer �о��� (PSI) �� ASML ���о���Ա����ʹ�ø��� EUV ���ϵͳɸѡ�� NA �ĸ��ֿ�ʴ�����о���Ա�ø��ֿ�ʴ��ͼ���������Ϳռ䣬ϣ����� 8nm ����ֱ��ʡ�

PSI ���չʾ������δ������Ӧ�̵� CAR �ͷ� CAR ��ʴ���Ľ����ʹ�ô�Լ 60mJ/cm² �� CAR ������PSI �� R&D EUV ϵͳ�� 13nm ���ദ�γ������������Ϳռ�ͼ�������� 12nm ���������Žӣ��� 11nm ������ͼ�����ݡ�PSI ���о�Ա Timothée Allenet ��һ���ݽ���˵��“�����Ѿ�����ѧ�Ŵ�ʴ�������շֱ��ʴ� 12 ������ߵ� 11 ���ף�ֻ���Ż��ײ㡣”

ͬʱ������ PSI ��˵������ 30mJ/cm² �����£����ӹ�̽��� 13nm �����ֳ����õ�ͼ�������� 12nm ��ͼ��̮�������������˹��ϡ�

Ȼ��ʹ�ò�ͬ�ļ����������������̽��ڵ��� 12nm �����ֳ����õ�Ч����“�� 11nm ��ھദ�������������Žӣ�Ȼ���� 10nm �����ֱַ���ƿ����”Allenet ˵��

�Ӻõķ�����˵������ 0.33 NA EUV ��������û��ͣ�Ͳ�ǰ���������ڸ��ơ����磬TEL ������ CAR �ͽ��������ʴ�����¹��ա�

“�ܶ���֮��Ϳ����/��Ӱ���������Ż��ĵײ㱡Ĥһ����ʾ�� CAR ͼ��̮��ԣ�ȵĸ��ơ��Ż��ĵײ�����˽��������ʴ����ȱ���ܶȡ������ʹֲڶȣ�”TEL �� Kanzo Kato ˵��

����

���� EUV ����Ҳ�ڿ����У����籡Ĥ����Ĥ���ڸ�����Ĥ����ֹ�������������ϡ�

ASML �������µ� EUV ��Ĥ�����ͬʱ��Imec ��̼���ܱ�Ĥ�� ASML �� EUV ɨ��������ʾ�� 97.7% �����ʡ����ںͶ�ڱ�Ĥ������ǰ;�ġ�

“�������͵ı��ֶ��ܺã��� CD �����ԡ�LWR ��ҫ�߷��棬������Ĥ�ο���ȣ���������С�����ݲ�õ���Щ��Ĥ�� EUV ���շ�Χ�� 95.3% �� 97.7%��Ԥ�Ƽ������������ӣ�”Imec ������Ա����Ҫ��Ա Emily Gallagher ˵��

�������ʣ��ܶ�������Ϊ����ֵ�� EUV ���������������������в����Ƿ�λ��оƬ�����̶���ʾ��2023 �꼰�Ժ��оƬ������Ҫ����ֵ�� EUV��

������ˣ��з��ɱ��Ÿոտ�ʼ�ѻ���û�ж������������Щϵͳ�����⣬���д��۲���ǣ�High NA ��̻���ʱ����Ͷ��������

|