正文内容 评论(0)

承接上文,在我们走进Graphics Core Next全新架构之前,先来简单回顾一下以往AMD显卡VILW架构的一些要点。

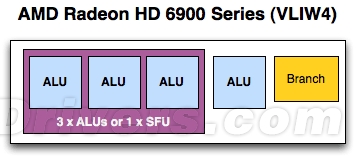

在过去的AMD的统一渲染架构中,基本的运算单元是流处理器单元(Streaming Processor,SPU)。我们知道,除了Cayman(调整为VILW4)核心以外,AMD从R600开始所有的GPU都采用了VLIW5架构(VLIW,超长指令流)。顾名思义,每一个流处理器单元有5个或者4个更基础的数学运算单元(算术逻辑运算器ALU和特殊函数运算器SFU,现在AMD统一称之为Radeon Cores),每一个数学运算单元都能在一个周期并行独立地执行相关指令。数学运算单元与寄存器(Registers)相连,后者主要负责存储输入数据、临时数值和输出数据,并不存放具体的指令,另外还有分支单元(Branch Units)负责指令流的重组和打包,这样就构成了一个完成了流处理器单元。

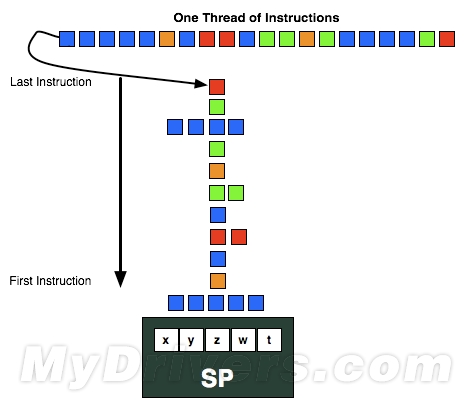

从设计方面来讲,VILW架构更擅长于并行执行相同的指令,这些相同的指令(线程)往往是被打散之后重新分组的wavefront(类似于NVIDIA的warp)。在AMD以往的实例里,wavefront是64个线程为一组,而指令流就是以wavefront来执行。理想的情况下,在一个wavefront中一组4或5个指令(类似于下图的蓝色指令)在流处理单元中并行完成,这样的执行效率最高达到100%,5个算数单元可以全部负载。但当较少的指令(比如1或2个,类似于下图的其它颜色指令),就会大大影响执行效率,因为此时只有1到2个运算单元负载。就这一点而言,VLIW架构始终难以在执行效率上达到完美,毕竟现实程序中的理想情况并没有那么多。

在3D图形进行渲染的过程中,VS和PS的主要工作就是进行X、Y、Z、W四个坐标运算和计算除R、G、B、A得出像素颜色。为了一次性处理1个完整的几何转换或像素渲染,GPU的VS和PS从最初就被设计成为同时具备4次运算能力的算数逻辑运算器(ALU)。 而数据的基本单元是Scalar(标量),就是指一个单独的变量,所以GPU的ALU进行一次这种变量操作,被称做1D标量。

与标量对应的是Vector(矢量),一个矢量由N个标量标量组成。所以传统GPU的ALU在一个时钟周期可以同时执行4次标量的并行运算被称做4D Vector(矢量)操作。虽然GPU的ALU指令发射端只有一个,但却可以同时运算4个通道的数据,这就是单指令多数据流(Single Instruction Multiple Data,SIMD)架构。

这种类似的SIMD架构可以追溯到R300(Radeon 9700)时代,而到了DX10统一渲染架构出现的R600(Radeon HD 2900),AMD采用VLIW5架构设计也是在此基础上进行的扩展和革新,因为当时的主要游戏市场依然被DX9占据,而游戏中采用的3D渲染程序也大都利于这种架构执行。但是随着时间的推移,新一代3D游戏和GPGPU(通用计算图形处理器)程序的出现,VILW架构的执行效率就开始出现问题了。

最后,值得一提的是调度问题。在CPU世界中,我们把指令丢给CPU并且安排它在必要的时候进行线程调度操作。但在VLIW的GPU架构里,线程调度是编译器的事儿。编译器对于已知程序的调度做地相当完美,但是对于未知程序的安排就不是很给力了。因为这种调度是静态的,并不能实时改变。再加上VILW架构对编译器的依赖相当之大,如此以来就更加雪上加霜。

那为什么讲AMD全新架构之前要说这些废话?很简单,没有这些我们不可能了解AMD新架构中做了什么,或者说为什么这么做。

本文收录在

#快讯

- 热门文章

- 换一波

- 好物推荐

- 换一波

- 关注我们

-

微博:快科技官方

快科技官方微博 -

今日头条:快科技

带来硬件软件、手机数码最快资讯! -

抖音:kkjcn

科技快讯、手机开箱、产品体验、应用推荐...