2021��7��27�գ�IntelCEO����·��������“Intel���ٴ��£��Ƴ̹��պͷ�װ�������Ϸ�����”�Ϸ����ݽ���

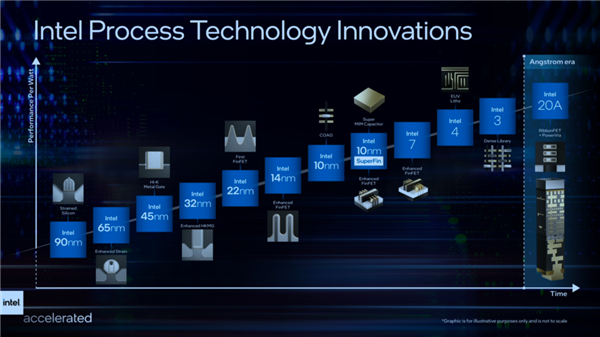

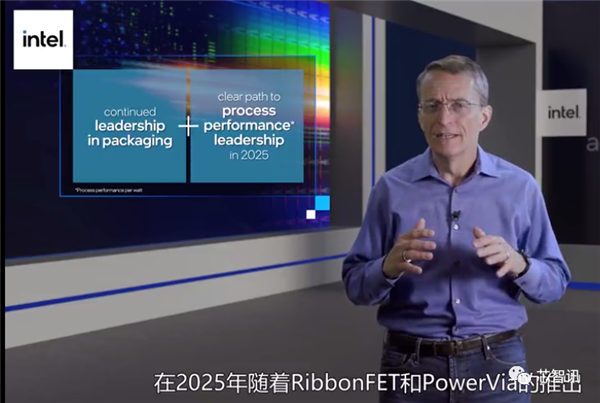

��������Ϸ������У�Intel�״ι�����δ��������Ƴ̹��պͷ�װ����·��ͼ������Intel�Ĺ��սڵ����������������ͬʱ������ȫ�µľ���ܼܹ�RibbonFET �ͱ�����ܴ�������PowerVia���Լ�ȫ�µ�Foveros Omni��Foveros Direct��װ������

���⣬�ھ�Բ����ҵ���棬IntelҲ�����ͻ�ơ��ڽ�������ϻ����ϣ�Intel�����Ѿ����ͨ�����20A���սڵ��ϵĺ�����ͬʱ���Ƚ���װ��Ҳ������ѷAWS����˺�����

һ��Intel����ȫ�¹��սڵ�������2024������20A�Ƴ�

������֪���ڰ뵼���Ƴ̹��սڵ�������ϣ�ͨ���ǰ��վ����դ������������������ԽСԽ�á�

�����ڶ���ǰ�����ٳ���Ϊ��ȡ���г�Ӫ���ϵ����ƣ����Ѿ��������ϸ��վ����դ�������������Ƴ̹��սڵ�ķ�ʽ������Ŀǰ��ʹ��ͬ���Ľڵ�������£�������ʵ��������Ҳ���ŷdz���IJ��졣

Ŀǰ�������ӽڵ�������������̨��������ǽ��꽫�����ڶ�����5nm���գ������Intel��˵���������ȵĵ�λ�����ǴӾ��������������̨�����5nm���������������ǵģ���Intel��������������ʾ���伴���Ƴ���7nm������������̨����5nm�൱��

��ǰIntel���Ƴ�10nm����֮ʱ���������ƶ��Ծ�����ܶ��������Ƴ̹������ܣ�����Ч���ѡ�

������Ϊ�˹��Ŀǰ���ҵ��Ƴ̹��սڵ�������ʽ��Intel�����IJ����ľ���Ӱ�죬�˴�Intel����δ���Ƴ̹���·��ͼʱ��Ҳ���乤�սڵ��������ʽ�������ع���

Intel�����˻��ڹؼ���������——�������ܡ����ĺ�����ȵ���������ϵ������һ���ڵ㵽��һ���ڵ����������ֵݼ�����ӳ�˶���Щ�ؼ������Ľ�������������

������Intel�Ƴ̼���·��ͼ��ʵ��ÿ���ڵ�Ĵ��¼����Լ��½ڵ���������ϸ��Ϣ��

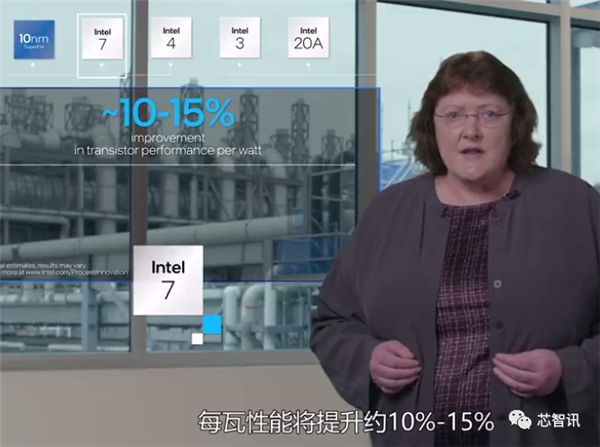

�� Intel 7

Intel 10����SuperFin���������ֲ��䣬������һ����“10����Enhanced SuperFin”���Ƴ̽ڵ㽫������Ϊ“Intel 7”��

�ݽ��ܣ�ͨ��FinFET������Ż���“Intel 7”��ÿ�����ܽ���Intel10����SuperFin����Լ10%��15%���Ż������������Ӧ�����ܡ����͵���IJ��ϡ������ܶ�ʴ�̼����������ͽṹ���Լ����ߵĽ�����ջʵ�ֲ����Ż���

Intel��2021���Ƴ�������ͻ��˵�Alder Lake�������Ȳ���“Intel 7”���գ�����Ԥ�ƽ���2022���һ����Ͷ���������������ĵ�Sapphire RapidsҲ�������“Intel 7”���ա�

�� Intel 4

��ǰ����֮ΪIntel 7�����յĽڵ㽫����������Ϊ“Intel 4”��

��Intel���ܣ���Intel 7��ȣ�Intel 4��ÿ�����������Լ20% ��ͬʱ��Ҳ��������ȫ����EUV��̼�����IntelFinFET�ڵ㡣��ǰ̨�����7nm EUV����Ҳֻ�Ǽ��ٲ��ֻ��ڲ�����EUV���ա�

���������ʱ���ϣ�Intel��ʾ��Intel 4����2022���°���Ͷ����2023���������Ʒ��������ͻ��˵�Meteor Lake�������������ĵ�Granite Rapids��

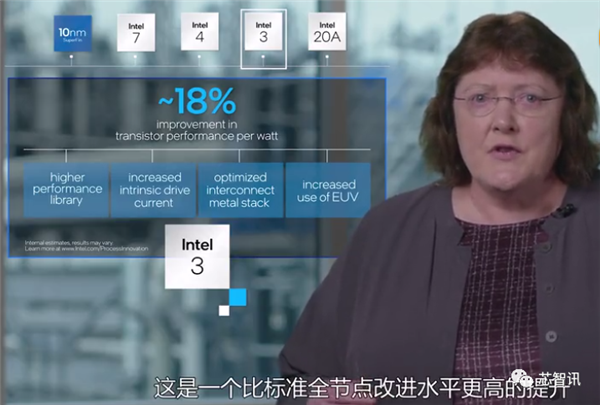

�� Intel 3

Intel 3 ������������FinFET�����ǰ����Intel 4��Intel 3����ÿ��������ʵ��Լ18%������������һ����ͨ���ı�ȫ�ڵ�Ľ�ˮƽ���ߵľ��������������

Intel�ƣ�Intel 3ʵ���˸����ܶȡ��������ܵĿ⣻�������������������ͨ������ͨ���裬�Ż��˻���������ջ����Intel 4��ȣ�Intel 3�ڸ�����������˸����EUV��ʹ�á�

Intel 3����2023���°��꿪ʼ������ز�Ʒ��

��ȻIntel��δ����Intel 3����Ӧ��Intel������ǰ�Ƴ̽ڵ㣬�����������̵��Ƴ̽ڵ㣬���Ǵ�Intel�Ľ���������Intel 3Ӧ���൱��Intelԭ����5nm�����ھ���ÿ�߹��������Ͽ����൱��̨�����3nm���ա���Ҳ��Ϊ��Ӣ�ؽ�����Intel 3 ������ԭ��

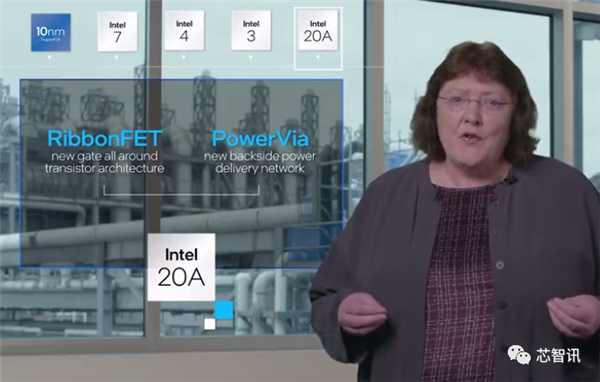

�� Intel 20A

�����Ƴ̹���Խ��Խ�ӽ���ԭ��ˮƽ��“1����”�ڵ㣬�����Ƴ̵��Ż�������������Խ��Խ���ѣ���ˣ�Intel���ٶȸı�������ʽ������Intel 3֮�����һ���ڵ㽫������ΪIntel 20A��20���ף����Ը��õط�ӳ��Ϊϸ���ϵĴ��¡�

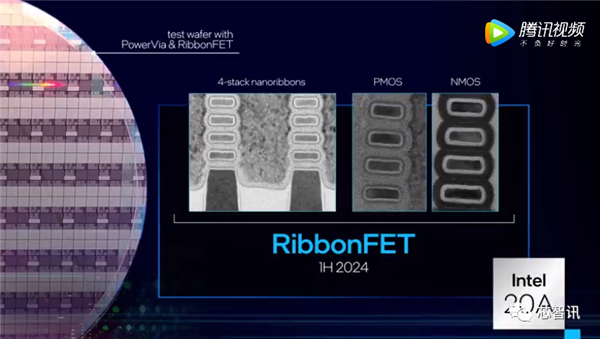

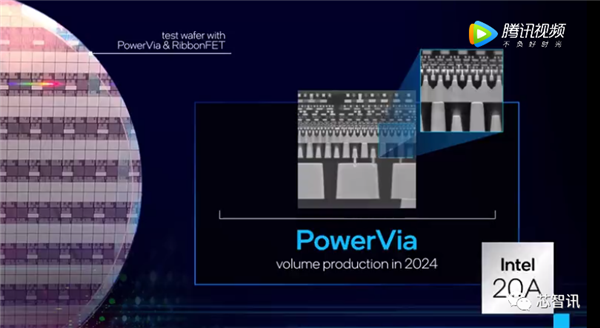

��Ϊ��ʵ��Intel 20A�Ƴ̣�Intel��������ȫ�µ�����ͻ���Լ���PowerVia��RibbonFET��

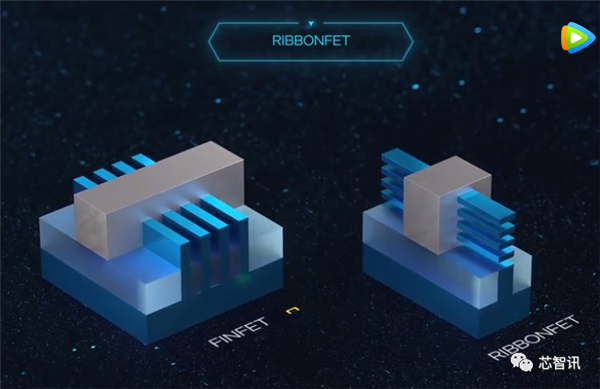

��νRibbonFETʵ���Ͼ���Intel�з���Gate All Around��GAA������ܡ�Intel��ʾ��RibbonFET���ṩ����ľ���ܿ����ٶȣ�ͬʱ�Ը�С��ռ�ÿռ�ʵ��������ṹ��ͬ������������������Intel��δ������GAA����ܼܹ���̨���硢���ǵ�GAA������

������ΪIntel�ṩ����ʾ������������������ʵ�ʲ�Ʒ��̬

����֮ǰ��������ʾ��̨���罫����õ��͵�GAA��ʽ——GAAFET�ǣ�Gate-all-around FETs���������õ��������߹�����ƣ�������������������դ����ȫ����������դ���Թ����Ŀ����Ը��á����֮�£���ͳ��FinFET ������3 �汻դ����Χ��GAAFET �ܹ��ľ�����ṩ��FinFET ���õľ������ԣ�������ijЩդ�����ȵ���������Ҫ������ͬ�ȳߴ�ṹ�£�GAA �Ĺ�����������ǿ�����ߴ���Խ�һ������

������������Ϊ���������߹�����Ʋ������ӣ��Ҹ����ijɱ�����Ҳ�������档��ˣ����������һ��ȫ�µ�GAA��ʽ——MBCFET��Multi-Bridge-Channel FET������-ͨ����ЧӦ�ܣ������ö��ѵ�������Ƭ�����GAAFET�е������ߡ���������Ƭ����ѱ��о�����IMEC����FinFET �ܹ�������Ʒ���д����о�������IBM �����Ǻ����º�����չ��

����Intel��������ʾ����������Intel���ܲ�������������GAA������Ƭ�ܹ���ơ�

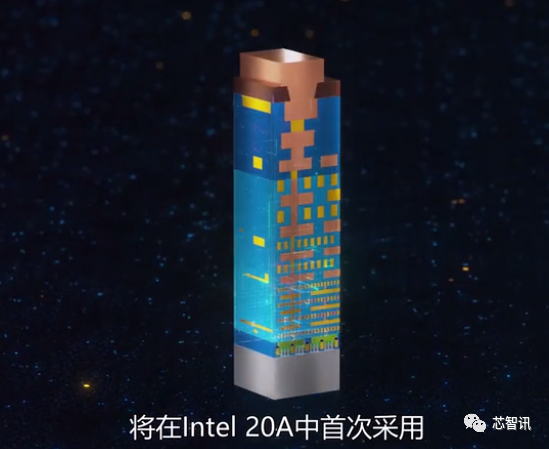

����PowerVia������Intel���С�ҵ����������ܴ������硣��ͳ�Ļ����������ھ���ܲ�Ķ������л������ɴ˲����ĵ�Դ�ߺ��ź��ߵĻ��죬�����˲���Ч�ʵ��µ����⣬��Ӱ�����ܺ��ġ��Դ�Intel�����Եİѵ�Դ�����ھ���ܲ�����棨����Բ�ı��棩��ͨ��������Բ����ĵ�Դ�����������ڳ��������Դ�����Ż��źŲ��߲�����ʱ�ӣ�ͨ�������´��ͽ����ţ�Ҳ������ʵ�ָ��õĵ��ܴ��䣬��ʹ��Intel���Ը��ݲ�Ʒ��������ܹ��Ļ���������Ż���

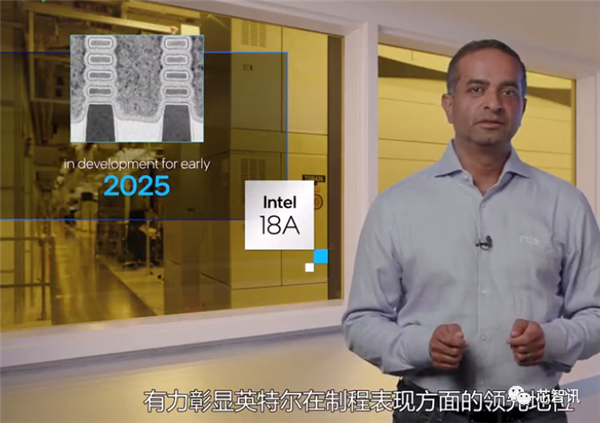

����Intel��Ԥ�ƣ���Intel 20A�Ƴ̽���2024���Ƴ������⣬Intel��¶������2025���Ƴ�18A�Ƴ̡�

Intel�����ܲü漼�������ܾ���Ann Kelleher��ʿ��ʾ��“Intel�����ƾõ��Ƴ̹��ջ����Դ��µ���ʷ����Щ���¾���������ҵ�ķ�Ծ�����������˴�90����Ӧ�����45����K����դ���Ĺ��ɣ�����22����ʱ��������FinFET��ƾ��RibbonFET��PowerVia�����Լ�����Intel 20A����Ϊ�Ƴ̼�������һ����ˮ�롣”

��Intel�����ܲü漼�������ܾ���Ann Kelleher��ʿ

�������Ȳ���High-NA EUV����

�����⣨EUV����̼��Dz��ø߶ȸ��ӵ����ͷ��侵��ѧϵͳ����13.5���ײ����Ĺ�Խ����Ӷ��ڹ�Ƭ�Ͽ�ӡ��С��ͼ������ĿǰASML��ȫ��Ψһ��EUV��̻���Ӧ�̡�ĿǰҪʵ��7nm���µ��Ƚ��Ƴ̣�������Ҫʹ��EUV��̻���

��7nm���տ�ʼ�����ֹ����Ѿ�������NA(Numerical Aperture)=0.33��EUV����豸����ͨ�����Ͳ�����ʵ��5nm���գ�������2nm�Ժ�ij���ϸ���գ���Ҫʵ�ָ��ߵķֱ��ʹ���豸��

IntelҪ��ʵ��20A�Ƴ̣�����Ҫ������ASML����һ������ֵ����High-NA����EUV��̻���

ASMLȥ���Ѿ������High-NA EUV����豸NXE��5000ϵ�еĻ�����ƣ��ƻ���2022��������ҵ����

Intel��ʾ�����������Ȼ��ҵ���һ̨High-NA EUV��̻���ͬʱҲ����ҵ���ҽ�High-NA EUV��̻�Ӧ�õ��������ڵij��̡���Ҳ��Intel���Ƴ̹������ܹ��ػ����ȵ�λ�Ĺؼ���

����2024�곬Խ̨����

�ӹ���������Ƴ̽ڵ������ʱ��������Intel���Խ��꿪ʼ����Intel 7 �Ƴ̣��˺�ÿһ�꽫���Ƴ���һ����ȫ���Ƴ̣������֮ǰIntel�����Ѿ������崵�“Tick-Tock”����ɱ�����������Intel��������Ϣ���佫��2025������20A��20���ף��൱��2nm���Ƴ̡�

���Intel20A�Ƴ��ܹ����������Ļ�����ô���ɽ�����̨����Ľ��ࡣ����̨����Ĺ滮����2022�꽫������3nm�Ƴ̣����2024������2nm�Ƴ̣���̨�����1nm��δ�������Ϣ��Ҳ����˵��Intel�������2024���20A�Ƴ̣��Ӷ�ʵ�ֶ�̨����ķ��������վ�����ܶ���������Intel20A�����Ͽ����൱��̨�����1nm�Ƴ̣������³�Ϊ�����ƶ�Ħ������ǰ���������ҵ��

“Ħ���������ڳ�����Ч������δ��ʮ������Խ‘1����’�ڵ�Ĵ��£�Intel����һ��������·��������˵�����Ԫ�����ڱ�֮ǰ��Ħ�����ɶ�����ʧЧ��Intel���������ù���������������ƽ����¡�”Intel��˾CEO����·������dz������ĵ�˵����

�ġ��Ƚ���װ�����ٶ�����

����Ħ�������ƽ����ٶȵķŻ����Լ��Ƚ��Ƴ����ܹ������ľ���Ч�������٣������������٣��ɱ�ȴ����������������Ƚ���װ�����Ѿ���Ϊ�˼����ƽ�Ħ�����ɵľ���Ч�����Ҫ�ֶΡ�

Ŀǰҵ�����еĶ�оƬ�Ƚ���װ�ܹ�������ԭ����ʹ�������Ƴ̹���������ͬIPģ�飬Ȼ��������ַ�װ��ʽ����һ����װ��ʵ�ֶ��оƬ���Լ���СоƬ֮��ĸߴ�������ʱ�ӵĸ��ٻ���������һ���칹����ƽ̨��ͬʱʹ������оƬ��װ��ʵ�����Ƶ�оƬSoC�����ܣ����dzɱ�ȴ������ڵ�оƬSoC��

��Ϊ�Ƚ���װ����������ҵ��Intel����2017��ʵ���˻���2.5D��װ����EMIB��Ƕ��ʽ��оƬ�����Žӣ���Ʒ�ij�����Sapphire Rapids�ǻ���EMIB����������������Intel��ǿ�������IJ�Ʒ��

Intel��ʾ����Ҳ��ҵ�����ṩ�����뵥Ƭ�����ͬ���ܵģ����������������ֳߴ����������Sapphire Rapids֮����һ��EMIB�����ཫ��55��������45�ס�

�����2018�����Intel�ܹ��ջ�ϣ�Intel�Ƴ���ҵ���״���3D��оƬ��װ����——Foveros 3D������ʵ������оƬ�϶ѵ���ͬ�Ƴ̵���оƬ����ǰֻ�ܰ���оƬ�ʹ洢оƬ����һ����Ϊ�м�Ĵ���������Ҫ��Ҫ��һЩ����Foveros 3D����Ѳ�ͬ�Ƴ̵���оƬ�ѵ���һ��ʵ�־�Բ����װ����Ƭ��Ļ�����϶ֻ��50μm��ͬʱ�ɱ�֤���ӵĴ����㹻���ٶȹ��졢���Ĺ��ͣ�����3D�Ķѵ���װ��ʽ�������Ա��ֽ�С�������

��Intel���ܣ�Meteor Lake���ڿͻ��˲�Ʒ��ʵ��Foveros�����ĵڶ������𡣸ò�Ʒ����36�����࣬��ͬ��Ƭ�ɻ��ڶ���Ƴ̽ڵ㣬����ƹ��ʷ�ΧΪ5-125W��

����EMIB��Foveros 3D�ȷ�װ����֮�⣬��2019��7���������ɽ�ɽ���е�SEMICON West����ϣ�Intel�ֹ�����������ȫ�µ��Ƚ�оƬ��װ������Co-EMIB��ODI��MDIO��

Co-EMIB�������ø��ܶȵĻ�����������EMIB 2D��װ��Foveros 3D��װ���������һ��ʵ�ָߴ��������ģ��Լ��൱�о�������I/O�ܶȡ�

ODI��Omni-Directional Interconnect������ȫ��λ��������������Ϊ��װ��СоƬ֮���ȫ��λ����ͨ���ṩ���������ԡ�

MDIO��Multi-Die IO����������Ƭ�����������AIB�����������ߣ��Ľ����棬ΪEMIB�ṩһ��������SiP PHY���ӿڣ��ɻ������СоƬ��

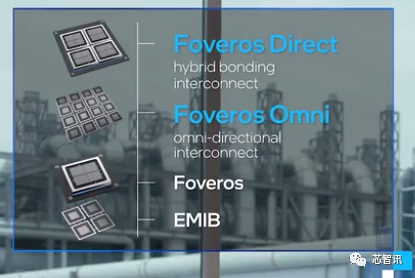

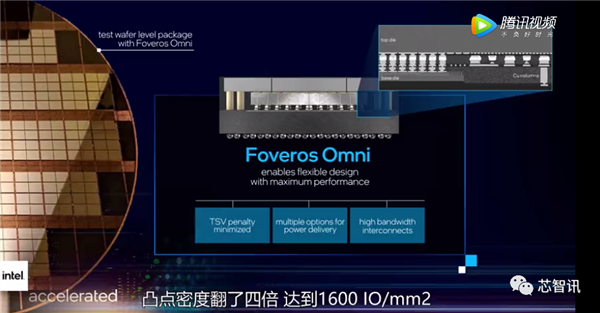

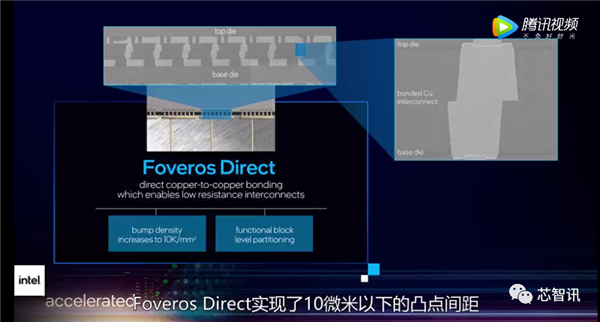

�ڽ�������ϻ����ϣ�Intel���Ƴ���ȫ�µķ�װ����Foveros Omni��Foveros Direct��

�ݽ��ܣ�Foveros Omni��������һ��Foveros������ͨ��������3D�ѵ�����Ϊ��Ƭ����Ƭ�Ļ�����ģ�黯����ṩ�������Ƶ�����ԡ�Foveros Omni������Ƭ�ֽ⣬�����ڲ�ͬ��Բ�Ƴ̽ڵ�Ķ����Ƭ������Ƭ��ϴ��䣬���ܶȷ����ı����ﵽ��1600 IO/mm?��

��Foveros Directʵ������ֱ��ͭ��ͭ���ϵ�ת�䣬������ʵ�ֵ͵��軥������ʹ�ôӾ�Բ�Ƴɵ���װ��ʼ������֮��Ľ�������ô��Ȼ��Foveros Directʵ����10�����µ����࣬ʹ3D�ѵ��Ļ����ܶ������һ����������Ϊ��������Ƭ����������µĸ��������ǰ����ʵ�ֵġ�

Intel��ʾ��Foveros OmniԤ�ƽ���2023���õ������IJ�Ʒ�С�Foveros Direct���Ƕ�Foveros Omni�IJ��䣬Ԥ��Ҳ����2023���õ������IJ�Ʒ�С�

�塢Intel����������ͻ��

�ڽ����3�µ�������Ϊ“Intel�������Թ��̼�����δ��”��ȫ��ֱ����ϣ������ε�IntelCEO��������Intel��IDM 2.0ս�ԣ�����Ͷ��200����Ԫ�������½�������Բ������������Intel�Ĵ�������IFS����

�����ڴ���ҵ����˵����Ϊ�ؼ����������ؾ��Dz��ܺͼ�����

�ڼ����ϣ�IntelĿǰ���Ƚ���װ����������ҵ�����ȵ�λ����ӵ�ж�����м������������Ƚ��Ƴ̼����ϣ�Intel���̨���紦������λ������������Intel�������¹�����·��ͼ���������һ�ж��ܹ����ռȶ���ʱ��ڵ���ʵ�Ļ�����ôIntel������2024�����Ƴ̹�����ʵ�ֶ�̨����ķ�����

Intel�ڽ���Ļ����϶����ʾ��Intel���Ƚ���װ���Ƚ��Ƴ̹��ս���ȫ�����š�Ҳ����˵��������оƬ���̶����Բ���Intel���Ƚ����Ƴ̼���װ�������������Ǿ��кܴ��������ġ�

�ڽ���Ļ����ϣ�IntelҲ�����Ѿ�������ѷǩԼ������ѷ����Ϊ�Ҳ���Intel��������ķ�װ��������ͻ���

���⣬�ھ�Բ�������棬Intel������ͨ�����Ϊ��������Intel20A�Ƴ̹��յĿͻ���Ҳ����˵����ͨ2024����Ƴ����콢оƬ����Intel��20A�Ƴ̹��մ�����

ǰ���ᵽ�����ڴ���ҵ����˵������Ҳ�Ǽ�Ϊ�ؼ���һ�����ڽ���3�£�Intel����Ͷ��200����Ԫ����������ɣ�����½�������Բ��֮����5�£�Intel��Ͷ��35����Ԫ��������ī�����ݵ�Rio Rancho������������������100����Ԫ����ɫ���˽��µľ�Բ�������գ�Intel �����˶Ը�˹����ӷ�⳧Ͷ�ʣ������2020 ��12�µ�3.5����Ԫ����߳���70%��6 ����Ԫ��

���µ���Ϣ����ʾ��Intel�ƻ�Ͷ��200����Ԫ�ڶ��ŷ�˳�Ա������оƬ������ĿǰIntel��˾������˵��ϣ��Ӯ��ŷ�˶Ը���Ŀ�IJ���������֧�֡�

�ڽ���Ļ����ϣ�IntelCEO������¶�������ڽ������һ��������ŷ��������Ͷ�ʲ��֣�“����һ������֧�ִ��;�Բ���ľ�Ͷ��”��

��һϵ�е�Ͷ�����ɽ���������Intel�ھ�Բ������Ƚ���װ����IJ��ܹ�Ӧ�������Intel����ҵ��ĺ�����չ�dz��ؼ���

������Ҫָ�����ǣ�����Intel������ͻ���Լ�����Ҫ��Intel���ո��ݺ�����ɣ���ݵĹ���������

“Intel��������Ƴ̺ͷ�װ������δ�����д��£�Intel�����ռȶ������Ƴ���Щ���¼�����Intel�������dz�ɫ�ļ����������㷺����ҵ����������������֮��ǰ����ҵ�����Intel�Ļع鷴Ӧ���ҡ�����˵��Intel�Ĵ���ҵ���Ѿ����”������dz��˷ܵ�˵����

|