��������������RISC��������Ȩ����MIPS��ʽ��������һ����ƷAptivϵ�У�����ProAptiv��interAptiv��microAptiv����������⾺������ARM��������Ʒ�ߡ�����Ӳ����վAnandtech�ڵ�һʱ���õ���MIPS�ṩ�ĵ�һ�����ϣ����ļ�ΪAnandtech��������ԭ�ĵĶ������ݱ���档

�����ֻ���ƽ���������֮��Ӣ������ARMƾ����ִ�������ͼ�κ���IP��Ȩռ��������г��ľ�������ݶ��ARMҲ����һֱ�ڳ�����Ϸ���ù�˾���ͬ���MIPSͬ��������RISC����������Ȩҵ��֮ǰMIPSƾ����Broadcom����ͨ����Sigma Designs����Ȩ�Ѿ����������˼�������/�����е�������������ARM������MIPSҲ������Ѹ���������ƶ�/ƽ���������š�

����ʱ��5��10�գ�MIPS��ʽ�������µĴ�����IP���ļ���——Aptivϵ�С���ARM��Cortex���ƣ�Aptivϵ�в�Ʒ���Ǹ߶����Ͷ����з�Χ�����������г����ṩ�����ܾ���ARMͬ����Ʒ���ƣ���������MIPS��ʽ����������IP��Ȩ��ս���ŽǴ��졣

��ǰMIPS�����IP���ķ�������Ϊ2010��9��——MIPS 1074Kϵ�С�����ʱ����ARM�Ѿ��ٷ�������Cortex-A15��Cortex-A7���Ƚ��������ARM����Cortex-A15����TI�������������ĵ�OMAP 5֮���Լ�Cortex-A5��Cortex-M4�Ŀ��Ʒ��Aptivϵ�е�������Ա��������һ��һ�����ԡ�

�������۷��棬MIPS��ʾĿǰ�ı�DMIPS/MHz/�����������ŶȲ��ߡ��ù�˾��ʾCoreMark���ܿ����ۺ��ĵ�������������MIPS��Ʒ�����о��б�ARM���ߵ����ܡ�CoreMark��Ҫͨ�����Զ�/д��ϲ����Լ�������������ܣ�����ʹ�ü���ANSI C�����д����x86������ͨ��gcc�����С������16K��������վAnandtech��ʾ��MIPS����CoreMark��ƫ����һ���������Ͼ����ܸ��÷�ӳL1�����Լ�Ԥ��ȡ�����ܡ���Ŀǰ����û��Cortex-A15��CoreMark���ݣ�����Ծɲ���DMIPS/MHz���бȽϡ�

MIPS������Aptivϵ���ܹ������������——ProAptiv��interAptiv��microAptiv������ǰ���߿�ѡ�������ã�����������proAptivΪ6��interAptivΪ4������Ͷ˵�microAptiv��Ϊ�����ġ�

�������ű��������ڶԱ�MIPS��ARM����ȫϵ�в�Ʒ�����ܣ�ע��������Ҫ���������������Լ�����Ķ�λ���࣬������ʵ��������������Cortex-Aϵ�ж�ӦMIPS proAptiv��Cortex-Rϵ�ж�ӦinterAptiv��Cortex-Mϵ�ж�ӦmicroAptiv��

|

MIPS��ARM�߶˲�Ʒ�ߺ������ܶԱ�

|

|

MIPS

|

DMIPS/MHz/Core

|

ARM

|

|

proAptiv

|

3.5

|

Cortex-A15

|

|

|

2.5

|

Cortex-A9

|

|

1074K

|

2.03

|

|

|

74K

|

2.0

|

Cortex-A8

|

|

|

1.9

|

Cortex-A7

|

|

|

1.57

|

Cortex-A5

|

|

M24K

|

1.46

|

|

|

|

1.24

|

ARM11

|

|

|

1.14

|

ARM9

|

��ȻMIPS��interAptiv��λ��Cortex-A5/A7/A9�ľ������֣����������ڲ�����ECC֧�ֵ�һЩ���ԣ������Cortex-Rϵ�����ܶԱȸ���һЩ�����߹ٷ����г���λ������ͬ——�������Լ�������ȫ/����ϵ���Ƶ�Ӧ�á�

|

MIPS��ARM�ж˲�Ʒ�ߺ������ܶԱ�

|

|

MIPS

|

DMIPS/MHz/Core

|

ARM

|

|

|

2.5

|

Cortex-R7

|

|

interAptiv

|

1.7

|

|

|

|

1.66

|

Cortex-R5

|

|

34K

|

1.62

|

Cortex-R4

|

|

1004K

|

1.5

|

|

|

24K

|

1.46

|

|

������������������MIPS microAptivϵ�еĶ�����ARM Cortex-Mϵ�С�

|

MIPS��ARM�������������ܶԱ�

|

|

MIPS

|

DMIPS/MHz/Core

|

ARM

|

|

microAptiv

|

1.56

|

|

|

M14K

|

1.5

|

|

|

M4K

|

1.3

|

|

|

|

1.25

|

Cortex-M3/M4

|

|

|

0.9

|

Cortex-M0

|

|

|

0.8

|

Cortex-M1

|

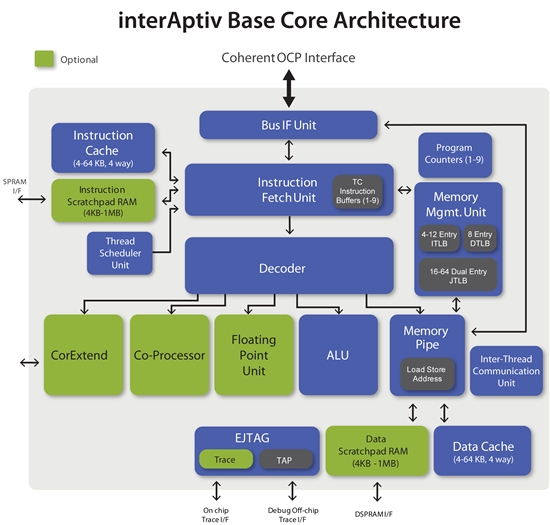

����������������MIPS�˴��·����Ĵ�����һЩ�ܹ�ϸ�ڣ�

proAptiv�ܹ�����

proAptiv�����������ӵ��1-6������������ÿ�����ĵ������Ϊ��Cortex-A15��һ�������Χ��Ⱥ���Ѿ����˱�ʾ��̾����������һ��Ҳ������ȫ�����ܣ���ǰҵ���Ѿ��в�����ʿ����ARM Cortex-A15������������Ƶ������Ǵ��˵㡣MIPS��Anandtech��ʾ������ARM����Cortex-A15�ľ�����û���ϸ�涨���������ֵֻ�ǹ��ơ�һ������ı�ֵ������ȥCortex-A15��NEON�����ֵ֮�����������MIPS proAptiv������ģ��32bit SIMD���棨DSP ASE���ǿ�ѡ���ֶ��DZض����ɡ�

ÿ��proAptiv���Ķ���һ�ų�������superscalar���ܹ���֧������ִ�е�CPU�������ڿɽ���4�������Լ�2��������������ؼ���TLB��ҳ�����壩��Ӧ���Լ�֧·����/Ԥ��ĸĽ�ʹ��proAptiv�Ա��ϴ�1074Kϵ��������߳���60%����FPU���־���dual-issue���ԣ�����Ƶ�ʺ�CPU��ͬ��

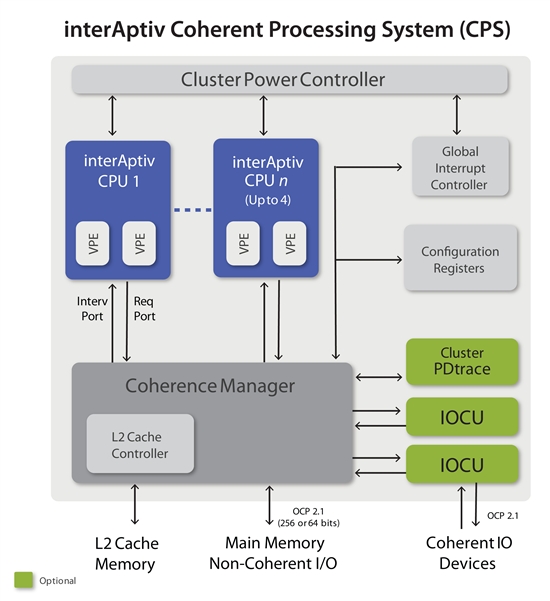

proAptiv��interAptiv���廹������EVA��Extended Virtual Addressing����չ���⻯Ѱַ�������������õع������ÿռ䡣������Cortex-A15����ЩIP�߱�һ��coherence manager�Լ����ϵ�L2�����������֧��ECC����֮ͬ����Cortex-A15����Ƽ���֧��32���ģ���proAptiv�������֧��6��������˼�IJ�����proAptiv��Coherent Processing System��CPS)�ɸ��ݸ��ؿ��Ƹ������ĵĵ�ѹ/Ƶ�ʵȣ�������ARM��Cortex-A15�������big.LITTLE��С���Ľ��ܲ��ԡ�����һ�㲻ͬ��Cortex-A15�еĽ���״̬���к�����2�����ĵ�Cortex-A7���ֻ�TI��OMAP 5��ʹ�õ�Cortex-M4����MIPS��proAptiv��������ÿ�����Ķ����ڳ��͵�ѹ/Ƶ���¹�������˽��ܺ��ľ���������������ÿ�����ĵ����ҲС��Cortex-A15��

|

�ܹ��Ա�

|

|

|

MIPS proAptiv

|

ARM Cortex-A9

|

��ͨKrait

|

ARM Cortex-A15

|

|

Decode

|

3-wide

|

2-wide

|

3-wide

|

3-wide

|

|

��ˮ�����

|

13��

|

8��

|

11��

|

15��

|

|

����ִ��

|

֧��

|

֧��

|

֧��

|

֧��

|

|

����FPU

|

��

|

��

|

��

|

��

|

|

��ý�崦������

|

32bit DSP ASE

|

��ѡ64bit MPE

|

128bit NEON

|

��ѡ128bit MPE

|

|

�Ƴ̹���

|

40nm/28nm

|

40nm/32nm

|

28nm

|

28nm

|

|

��������Ƶ��

|

1.2GHz

|

1.2GHz

|

1.5GHz

|

2.5GHz

|

����Ƕ��ʽӦ�ã�proAptiv�����ص��Ƕ��ڹ��ĵ������ԣ���ʱproAptiv���������Ƶ��Ԥ��ֻ��1.5GHz���ҡ�Anandtech�Ƹ���MIPS�����±�̬��1.2GHz�ĵ�������Ƶ������̨����40nm���յ���������ȡ�á������ͬ����28nm HP/G�Ƴ̣�proAptiv��Cortex-A15�ļ���Ƶ���൱����Ϊ2.0-2.5GHz��

interAptiv��microAptiv�ܹ�����

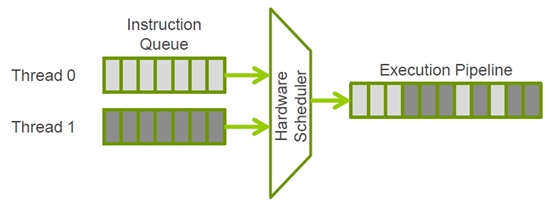

interAptiv��Ʒ���������ص���֧�ֳ��߳�——ĿǰARM��û��һ���Ʒ���볬�̼߳��������Ų���Intel Medfield Atom��Ʒ�������豸���У����볬�̼߳�������Ŀǰ�ճ�ʹ�õĸ��������ܵ�������ν�dz�������

MIPS��3��interAptiv���ĵ����ܱ������ƻ�������2��Cortex-A9/3��Cortex-A5���ģ���������ۺ�����Ҳ�����൱����ȻMIPS����������CoreMark���Է���interAptiv�϶�ռ���ơ���interAptiv�����Ʒ��CPUִ�й���Ϊ����߳����������ɼ����ڴ�����ӳٶ������ܵij���̶ȡ�

MIPS�����̽���ΪVPE��Virtual Processing Elements����interAptiv���ĵ���ˮ�����Ϊ9������֧������ִ�С���֧�ֶ��̵߳�IEEE 754��FPUΪ��ѡ����峧��/�û��ɸ����Լ������ơ�����DSP ASE��ý�崦�������Լ�EVA��չѰַ����Ҳͬ��Ϊ��ѡģ�顣���ܼ�������interAptiv��proAptivͬ��Ӧ��CPSϵͳ������proAptiv�Աȣ�interAptiv���ļܹ��Ľ��ܼ�������һ�������Ŀ����ڵ�������ȫ�رգ�Ƶ�ʽ�Ϊ0����L1ָ��+���ݻ�����ڴ�ʱ����ѡ��proAptivֻ������ѡ��L1ָ��档

��ʹ��̨����40nm G�������죬interAptiv��Ʒ�������Ƶ�ʿɴ�1GHz������һ��ģ��ͳ��̹߳�������������̹߳����е�Ӳ�����Ȳ���Ƶ�ʿɴ�1.2GHz��������ȥ����ý�崦������Ƶ�ʿɳ���1.5GHz��MIPS��ʾ��Щ�ο�ֵΪ“���”Ƶ�ʣ���ʱ���ıȴ������״̬����Ȼ���������Ȩ����ʵ�ʲ�Ʒ���ȡ�����û�����ѡ��

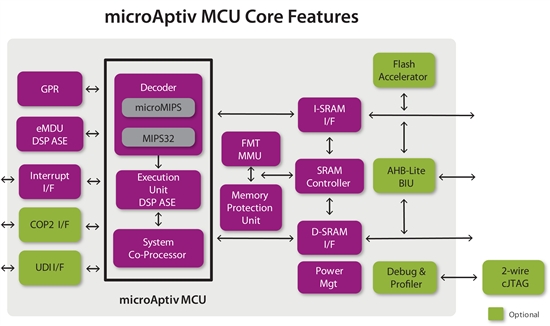

��Ӧ���ڹ�ҵ����������˵�microAptivϵ�в�ƷΪ��ǰM14k/c��“�����Ż�”�棬֧��microMIPS����ѹ��������������DSP ASE���棬�źŴ������ڸ��ͳɱ�����ɡ�

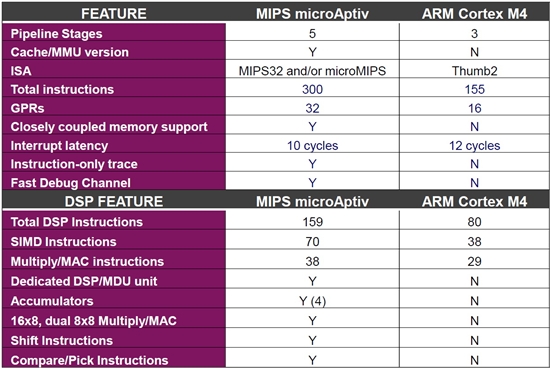

����5����ˮ�ߵļܹ�����Ƶ����65nm LP�Ƴ�����߿ɴ�400MHz��MIPSͬʱ�����˺�Cortex-M4�ĶԱȣ�

��Ȼ���Ա�Cortex-M4�����һ����������Ͽ϶�ҲҪ������90nm LP�Ƴ̹��յ������£�ARM������������Cortex-M4�����Ϊ0.17ƽ�����ף��������microAptiv MCU�����Ϊ0.42ƽ�����ס���MIPS��Anandtech���������ݷ�ͬ�����Աȣ���90nm LP��������Ż�����microAptivֻ��Cortex-M4�����0.01ƽ�����ס���֮��㹫˵��������˵�����������ܴ���ٷ���ֻҪ�и������Կ϶����ö�������������

��̸���ܽ�

MIPS��2010��9�·�����1074Kϵ�д�������ֱ������Ҳֻ��һ�ҳ����Ƴ���ʵ�ʵIJ�Ʒ����Ȼ�в��ټ�ǩ����IP��ȨЭ�飬������1074K��SoC����������һ��——eSiliconȥ����������GlobalFoundries 28nm�Ƴ̹��յ�1074K��Ʒ��Ƭ��ɣ��������ղ�Ʒ���л������������ʱ�䡣��һ�����ARMҲ��ͬ����Cortex-A15����2011��2�¾���������ʵ�ʲ�Ʒ����Ҫ�ȵ�2013�����

��Ȼ�߶˵�proAptic�����ܴ�����Cortex-A15�൱�����ܣ������ò��ź���˵MIPS�IJ���ʵ���е����ˣ������IJ��������û�д��������ϵ������Ǿͻ��Ϊ���ơ����˵��ǣ�MIPS��Ʒ�����幦�ĸ��ͣ���ARM��Ʒ������г���һЩ��ͬ������������������г��к�MIPSǩ����ȨЭ��ij��̹��٣��������������ͷ��ͨ�Ͳ�ͨ��������Ȩ��������ƶ��豸���ٷ�չ��ʱ�����ǿ��ܻ�����MIPS��Ʒ�ARM�Ŀ�ȱ�������߰�����ʵ������оҲͬ����һ��������

����Googleͬ��Ҳ��Ŀ��Ͷ����MIPS������Android NDK���º����°濪�����������ij�������MIPSƽ̨���ּ������������������������ARM��x86������Ӫ֮���MIPS��Ȼ�ռ䲢����̫��MIPS��õķ������Dz�Ҫ���������������г����Ƴ��������ܵĺ��ĺͳ��Դ����еͶ������ֻ�/ƽ������г�����һ�����ֶΡ����˵��ǣ��������MIPS�ĺ���������ڲ���Ŭ���������ϰ�ŵ�Ƴ���ȫ����Android 4.0ƽ����ԡ�

������ô˵����η�������proAptivϵ�в�Ʒ�����û������м�������ģ��ر����ڼ��������豸�ͻ�����������Щ�ط���������MIPS����ARM��ǿ���proAptiv�IJ�������Ҳ������MIPS�������Ѽ��г��ĵ���������interAptiv��microAptivϵ�жԱ�ARM�Ķ�λ�൱��Ʒ���ܾ������ƣ�interAptiv���г��̼߳�����microAptiv���м��ɵ�ǿ��DSP�������ڿ������г��������߾��в�С�����ơ�

Ԥ��proAptiv��interAptivϵ�к��Ľ���2012��������ʼ������ʽ�����Σ���microAptiv���ھͿɽ���������MIPS�Ѿ����ҳ��̽����ս�Ժ�����ϵ���ƹ��Լ�IP�ͼ��������ƶ�SoC���з��ٶȡ����ǽ�������ע����MIPS�ܹ�SoC�������Ľ�չ����ϣ�����ܾ����ó�ʵ�

|