正文内容 评论(0)

[Core和Yonah的不同点:(六)宏指令融合技术的应用]

所谓宏指令(Macro-Op),指的就是X86指令。通过宏指令融合技术可以使Core微架构在单位时间内把2条宏指令融合为1条微指令。这也就是为什么我们前文中提到Core微架构每个周期最多可以解码5条X86指令而实际只有4个解码单元。

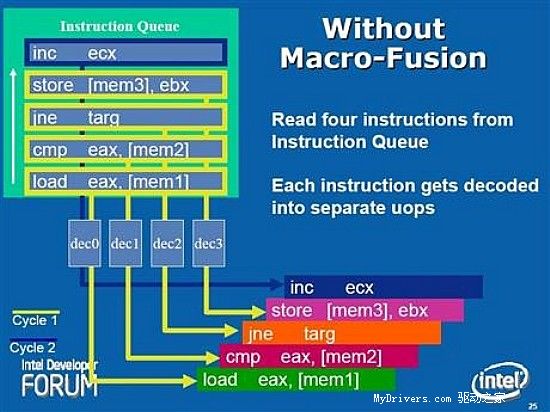

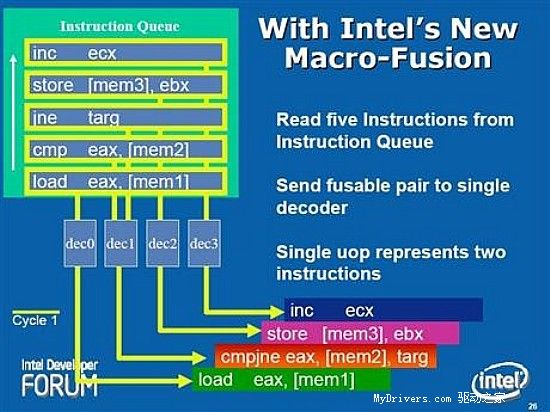

宏指令融合技术采用与否的示意图:

未采用宏指令融合技术

采用宏指令融合技术

从图中我们可以很明显地看到X86指令中的cmp指令可以与jmp指令融合,产生仅1条微指令。最后,4个解码单元中的任何一个都可以执行宏指令融合操作,然而每个周期最多只能有1个解码单元执行宏指令融合,所以最大的解码宽度为每周期5条X86指令,也就验证了我们前面所说的Core微架构只有4个解码单元每个周期却最多可以解码5条X86指令的说法。

很明显宏指令融合技术(Macro-op Fusion)的优点是降低需要执行的微指令的数目,因为执行单元只需执行更少的微指令,可以直接提高处理器性能。而实际上微指令缓冲区相当于容纳了更多的X86指令,乱序执行引擎可以从中更有效的发现能够并行的指令,有利于实现更高的指令级并行度。当然,这些优点虽然与微指令融合技术所带来的优点十分相似。但是,同时拥有宏指令融合技术和微指令融合技术使得Core微架构可以比Yonah微架构节省更多的执行单元资源和拥有更好的指令级并行度。不过具有讽刺意味的是,宏指令融合技术和微指令融合技术正在使得X86处理器的内核更加接近CISC架构(Complex Instruction Set Computer,复杂指令集计算机,在CISC微处理器中,程序的各条指令是按顺序串行执行的,每条指令中的各个操作也是按顺序串行执行的。顺序执行的优点是控制简单,但计算机各部分的利用率不高,执行速度慢)而不是 RISC 架构(Reduced Instruction Set Computing,精简指令集计算机,它是在CISC指令系统基础上发展起来的,有人对CISC机进行测试表明,各种指令的使用频度相当悬殊,最常使用的是一些比较简单的指令,它们仅占指令总数的20%,但在程序中出现的频度却占80%。复杂的指令系统必然增加微处理器的复杂性,使处理器的研制时间长,成本高。并且复杂指令需要复杂的操作,必然会降低计算机的速度。基于上述原因,20世纪80年代RISC型CPU诞生了,相对于CISC型CPU ,RISC型CPU不仅精简了指令系统,还采用了一种叫做“超标量和超流水线结构”,大大增加了并行处理能力。RISC指令集是高性能CPU的发展方向。它与传统的CISC相对。相比而言,RISC的指令格式统一,种类比较少,寻址方式也比复杂指令集少。当然处理速度就提高很多了)这与 Intel 当年推出 IA-64 架构(安腾Itanium是64位处理器,也是IA-64系列中的第一款,基于EPIC技术开发。最大的缺陷是它们缺乏与x86的兼容,而Intel为了IA-64处理器能够更好地运行两个朝代的软件,它在IA-64处理器上引入了x86-to-IA-64的解码器,这样就能够把x86指令翻译为IA-64指令。这个解码器并不是最有效率的解码器,也不是运行x86代码的最好途径,因此Itanium 和Itanium2在运行x86应用程序时候的性能非常糟糕。这也成为X86-64产生的根本原因)的想法越来越远。看来Intel确实是走下了很大的弯路,好在亡羊补牢为时不完。