正文内容 评论(0)

[Intel半导体工艺发展蓝图]

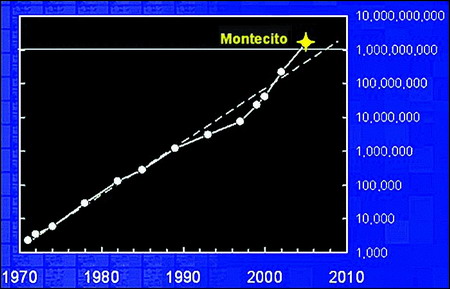

在介绍65纳米技术之前,我们有必要来了解一下英特尔在半导体制造工艺领域的发展计划。在下面这个处理器晶体管规模的曲线图中,我们可以看到英特尔基本上严格遵守摩尔定律,芯片的集成度保持18个月翻一番甚至更快的上升节奏。

目前,英特尔所拥有最高集成度的芯片应该是Montecito核心的Itanium处理器,Montecito集成两个CPU核心,缓存单元的容量达到26.5MB,而晶体管规模高达17.2亿个,超出了摩尔定律的定义。英特尔打算用90纳米工艺来生产Montecito,这不可避免使它的生产成本极其高昂,考虑到Itanium产品线的定位,90纳米的高成本也是可以接受的。再者,这也是目前65纳米工艺尚无法进入实用阶段的权宜之计。

在工艺发展上,英特尔有自己的一套严格计划,我们可以从下表中很清楚看到相关的细节。2001年,引入代号为Px60的130纳米工艺,晶体管门长度为70纳米,使用200/300毫米的硅晶圆加工生产。2003年,引入代号为P1262的90纳米工艺,晶体管门长度降低到50纳米,全面使用300毫米的硅晶圆。2005年,引入代号为P1264的65纳米工艺,晶体管的门长度只有35纳米,同样使用300毫米晶圆。而到了2007年,代号为P1266的45纳米工艺将被及时引入,晶体管门长度只有25纳米尺度。2009年,代号P1268的32纳米工艺导入,晶体管门长度降低到18纳米的惊人尺度。在这之后,硅半导体制造技术将会出现原子极限,但可以保证,至少到2009年,摩尔定律都是有效的。英特尔在研发65纳米工艺之时并没有忘记前瞻性的研究,例如EUV深紫外光光刻机技术,为2010年后半导体芯片准备的三门晶体管技术等等,在后文中我们也会对这些内容作一定的介绍。

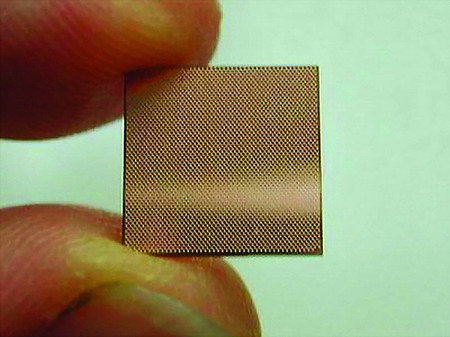

65纳米工艺制造的70Mbit容量SRAM芯片,面积只有110平方毫米。

可以看到,现在正处于从90纳米向65纳米转换的关口。英特尔的65纳米技术由位于俄勒冈州Hillsboro的英特尔90纳米开发工厂(称为D1D)开发,在今年8月份,它就宣布65纳米技术已经开发成功并制造出SRAM芯片样品。该SRAM的容量达到70Mbit(相当于8.75MB),包含了5亿多个晶体管,每个晶体管栅极(打开和关闭晶体管的开关)的尺寸只有35纳米,相当于目前90纳米技术的70%,人体的一个红细胞都比它大上100倍之多。另外,英特尔在晶体管内部使用了低K值(低介电常数)的新材料来提高芯片中的信号速度,而在晶体管之间栅极则使用厚度为1.2纳米的氧化物材料,有利于降低栅极电容,缓解电流泄漏的问题,最终有效降低芯片的功耗。在现有的90纳米工艺上,英特尔就没能解决这个问题,电流泄漏造成芯片功耗不降反增。此外,英特尔在65纳米工艺中成功开发出八个铜互联层结构,达到了相当高的工艺水平。毫无疑问,65纳米工艺令芯片的面积大大缩小,集成度也创下新高,所公布的70Mbit容量、65纳米工艺制造的SRAM芯片本身只占据110平方毫米的面积,若将容量降到4MB,那么芯片本身只需占据50平方毫米左右,即使加上两个CPU内核,一枚芯片所占据的面积也只有100平方毫米,成本比现在的Pentium 4还要低,这充分说明65纳米工艺的优越性。

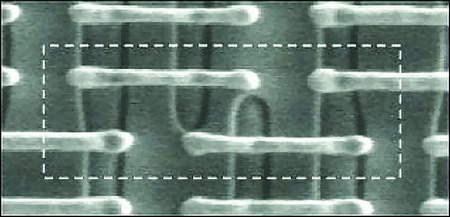

65纳米SRAM芯片的基本存储单元,白虚线区域的面积只有0.57平方微米。

本文收录在

#快讯

- 热门文章

- 换一波

- 好物推荐

- 换一波

- 关注我们

-

微博:快科技官方

快科技官方微博 -

今日头条:快科技

带来硬件软件、手机数码最快资讯! -

抖音:kkjcn

科技快讯、手机开箱、产品体验、应用推荐...