正文内容 评论(0)

[FB-DIMM的信息中转站]

缓冲控制芯片是FB-DIMM的中枢神经,它有一个专用名称:Advanced Memory Buffer,意为高级内存缓冲。前面我们提到,FB-DIMM的所有控制功能都是由它来实现,而不仅仅只是用于缓冲数据。下面,我们将深入其逻辑内部,剖析它的结构。

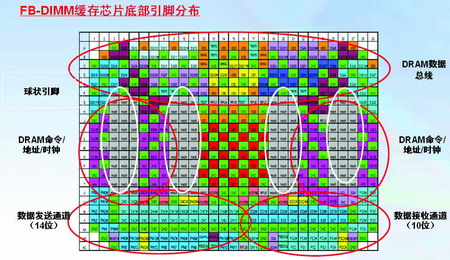

根据前面所述,我们可以将缓冲芯片的功能分解为串行总线传输、并行-串行数据互转、内存读写控制以及缓冲芯片通讯等四大部分,这些功能都有专门的逻辑单元一一对应。在串行总线传输部分,我们介绍过其不对等的设计,数据发送14bit,数据接收10bit。在缓冲芯片逻辑内,发送部分被称为“Northbound(北区)”,而接收部分则被称为“Southbound(南区)”,北南二区的总线控制职能分别由缓冲芯片中的“中转/合并(Pass through&Merging)”、“中转(Pass-through)”控制逻辑所掌管。而在同一个通道的多个FB-DIMM模组中,各个缓冲芯片的“中转/合并”逻辑直接串联,“中转”逻辑也与其他“中转”逻辑相连,二者泾渭分明。另外,因北区负责数据发送,来自后一条模组的数据在传给前一条模组的同时会被合并处理,这就是将控制部分称为“中转/合并”逻辑的原因。

并-串数据互转是缓冲控制芯片的又一个关键点。对于数据发送的北区,就是将从内存中读取出来的并行数据预先转换为串行数据流,它是由缓冲芯片的“串行转换逻辑(serializer)”来完成的。而对于北区接收到的数据,则是由“并行转换/解码逻辑(De-serializer &Decode Logic)”处理的,首先将串行数据转为对应的并行格式,然后将数据流包含的写入命令和地址信息进行解码,并据此完成写入操作。

毫无疑问,数据读取和写入操作的最终对象都是FB-DIMM模组内的内存芯片。我们在缓冲控制芯片的逻辑中发现,缓冲芯片与内存芯片的通讯完全是由“数据总线接口(Data Bus Interface)”进行统一掌管,它也是二者之间最主要的连接点。在读取数据时,内存模组中传出的并行数据经过数据总线接口后指派给上面的“串行转换逻辑”,得出的串行数据流被发送给内存控制器。而进行写入操作时,并行化后的数据也必须通过这个接口,再写入到指定的区域。显然,它承担的只是简单的转换控制工作而已,但从中我们可以看到,FB-DIMM模组芯片采用多少位的设计无关紧要,其实Intel可以将它设计为64bit,升级更为平滑,也可以设计为128bit模组来获得更高的性能,在现有技术条件下实现这样的目标可谓是轻而易举,而我们前面推测FB-DIMM系统的效能其实也都还是保守数字。

到此为止,整套FB-DIMM系统便能轻松运转起来了,在上述分析中不难看出,该缓冲控制芯片的结构并不复杂,功能单元相对简单,没有多大的设计难度,更多体现的是一种理念的创新。根据1.0版规范,该枚芯片将采用类似BGA的封装技术,芯片整体尺寸为24.5×19.5×2.15毫米,很容易便能安装到内存的PCB板上。从样品图中可以看出,该芯片的核心面积很小,量产后的制造成本很低。其底部一共有多达655个球状焊接信号点,分布井然有序。