正文内容 评论(0)

[FB-DIMM的中枢神经]

串行总线设计是FB-DIMM赖以拥有高效能的基础。实际上,Intel并没有另起炉灶从零开始设计,而是直接沿用了许多来自于PCI Express的成果,其中最关键的就是使用差分信号技术(Differential Signaling)。

关于差分信号技术,此前我们在介绍串行ATA、HyperTransport和PCI Express总线时都有过多方探讨,这里不妨进行简单重述。我们知道,现有各种并行总线都是以一条线路来传输一个数据信号,高电平表示“1”,低电平表示“0”,或者反过来由低电平表示“1”,高电平表示“0”。单通道结构的64bit内存需要使用64条金属线路来传输数据,双通道就需用到128条线路。当数据在线路传输时,很容易受到电磁环境的干扰,导致原始数据出现异常,如高电平信号电压变低,或低电平的电压变高,这些干扰都有可能让接收方作出错误的判断,导致数据传输失败。过去业界曾为这个难题大伤脑筋,当初硬盘数据排线从40针提高到80针细线(增加40根地线)就是为了降低传输干扰,但直到串行技术引入后问题方告解决。

与传统技术迥然不同,差分信号不再是以单条线路的高低电平作为“0”和“1”的判断依据,而是采用两条线路来表达一个二进制数据—数据究竟为“0”还是“1”取决于这两条线路的电压差。这样,即使受到严重的外来干扰,导致两条线路传输的电平信号发生较大范围的电压波动,但它们之间的电压差依然可以保持相对稳定,接收方便能够作出正确的判断。因此,差分信号技术拥有非常强的抗干扰能力,但因它需要占用两条线路,很难被引入到并行总线技术中,只有针对服务器应用的SCSI总线是个例外。

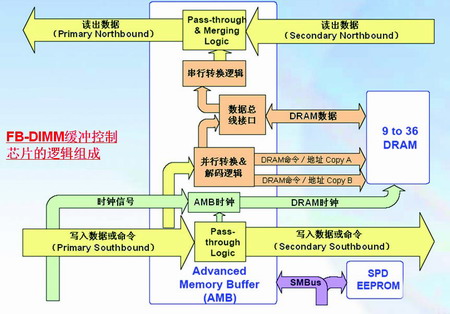

FB-DIMM借鉴PCI Express技术的第二个地方,就是其串行总线也采用了点对点结构。目前,DDR体系的并行总线无法在同一时刻同时发送和接收数据,二者根据指令轮流进行。然而FB-DIMM却可以在同一时刻同时发送和接收数据,奥秘在于它拥有两个串行通路,一个用于数据发送,一个用于数据接收。与之对应,FB-DIMM的缓存芯片有专用的发送控制逻辑和接收控制逻辑,数据读出操作和写入操作可在一个周期内同步进行。这实际上将内存系统的理论延迟时间缩短了一半,弥补了缓冲处理所造成的损失。较为特殊的是,FB-DIMM的数据发送总线与接收总线是不对等的,发送总线一共有14个线路对,一次向内存控制器发送14bit数据。而接收总线采用10位设计,每次只能够接收10bit数据。笼统地说,单通道的FB-DIMM模组就是24bit设计。这种不对等设计之前没有先例,但它却十分符合内存系统的客观实际。在大多数情况下,CPU从内存中读出的数据总是远远多于写入到内存的数据,与之对应,读取总线带宽高于写入总线的设计方案科学合理,而且十分经济。