正文内容 评论(0)

如果说Core 2 Duo的胜利奠定了多核发展的趋势,那么Core i系列绝对是将其发扬光大的一代,随后四核、六核、八核产品不断发力,整个处理器行业出现了欣欣向荣的局面。

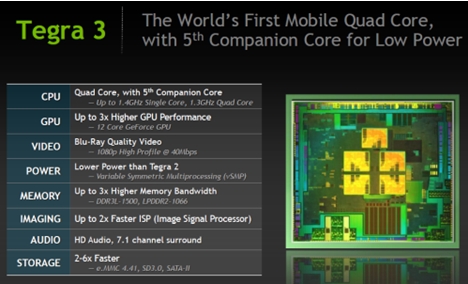

而受此背景熏陶的移动芯片业正在酝酿这样一种变革,2011年11月份NVIDIA正式发布了全球首款基于4+1核设计的Tegra 3芯片,产品首次将移动计算带入四核时代。

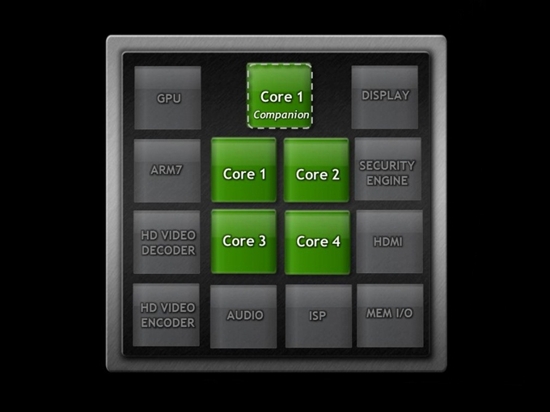

Tegra 3仍采用台积电40nm工艺制造,四核心最高频率1.4GHz,单核最高1.5GHz,CPU性能最高可达Tegra 2的5倍。不同于PC领域,移动计算芯片虽然迫切需要多核高效,但是面临的功耗依然不容小觑,而NVIDIA Tegra 3采用的超低功耗第五核心(协处理器)很好的解决了这一问题,每个内核包括32KB的数据缓存和32KB的指令缓存,另外四个内核共享1MB的二级缓存另外在Tegra 2时代由于删掉了可选的NEON协处理器,导致面对多媒体加速处理方面性能损失较大,为了弥补这一遗憾,NVIDIA重新找回了这一方案,NVIDIA命名为“companion core”,意即协处理器内核,集高性能、低功耗设计于一身的Tegra 3可以用完美来形容。

虽然Tegra在3D游戏及应用方面表现不俗,不过由于去掉了NEON,一些网页(Flash)等图形应用表现很糟糕,新的Tegra 3芯片吸取了这一经验,加入了全新的“companion core”内核,这样简单的图形应用以及多媒体处理器主要交由companion core负责,而大型的应用则交由4个Cortex A9内核以及图形单元处理,这样做的好处除了增强了芯片的处理能力,还提升了芯片的效能。

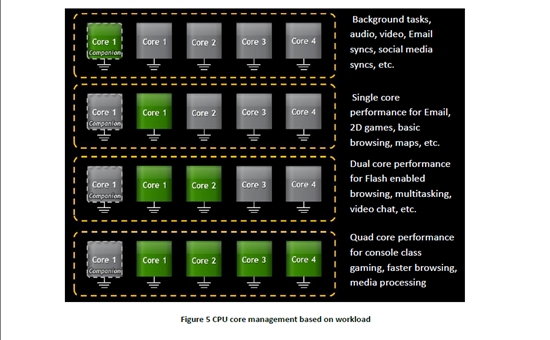

为了提高能效,NVIDIA还引入了新的Variable Symmetric Multiprocessing(vSMP)技术,即动态均衡多核调节,顾名思义就是根据任务的轻重情况动态调节内核的工作状态以达到节能的目的,当然在任务繁重的情况下,在TDP的调节范围内,也可以全面发挥四核的性能,以满足任务的需求。在后台运行、音频、视频、Email同步、社交媒体同步等应用时,仅调用“companion core”内核就可以满足需求,而当任务升级为2D游戏、地图应用等操作时,将启用1个Cortex A9内核以满足需求。

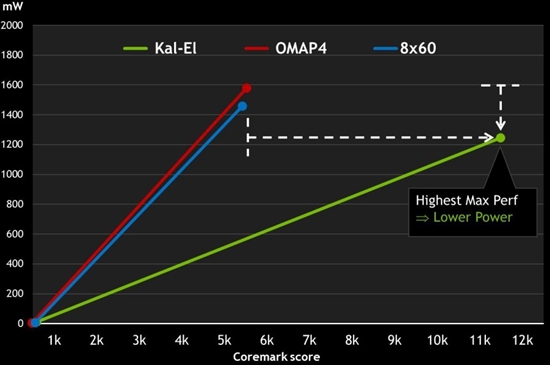

companion core是利用低功耗工艺技术设计而成的,然而却拥有同主核心相同的内部架构。因为它是利用低功耗工艺技术制造的,以低性能模式运行,所以它的功耗低于这些采用高速工艺技术制造的主CPU核心。在Tegra3处理器上测得的性能功耗比显示,协核心在500MHz以下工作时可实现高于主核心的每瓦特性能。因此协核心的最高工作频率不高于500MHz。

与协核心不同,CPU主核心需要以极高的频率运行才能实现高性能。因此它们是利用高速工艺技术制造而成的,这种工艺技术让主核心能够在较低的工作电压下将工作频率提升至极高的水平,因此主核心能够在不大幅增加动态功耗的情况下实现高性能。

vSMP技术通过利用协核心最大限度降低活动待机状态下的漏电功耗,同时利用四个主核心最大限度降低峰值工作频率下的动态功耗,从而可大幅降低整体功耗。根据使用场合,vSMP技术能够动态地启用和关闭CPU核心,从而在尽可能低的功耗下实现想要的性能。

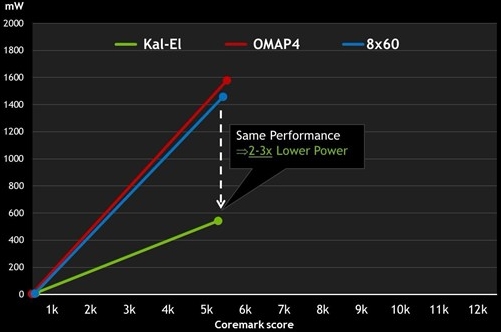

而得益于可变对称多重处理,Tegra 3虽然拥有5个核心,不过功耗却比单核芯片效能要高出2-3倍,正如一些基本的应用,单核就可以满足性能需求,所以整体功耗控制依然非常出色。

本文收录在

#快讯

- 热门文章

- 换一波

- 好物推荐

- 换一波

- 关注我们

-

微博:快科技官方

快科技官方微博 -

今日头条:快科技

带来硬件软件、手机数码最快资讯! -

抖音:kkjcn

科技快讯、手机开箱、产品体验、应用推荐...