正文内容 评论(0)

IDF的最后一天就是Intel的未来展望秀,CTO Justin Rattner同时宣布Intel将与美光联合开发一种新的DRAM技术,命名为"Hybrid Memory Cube"(HMC),针对未来在CPU发展进程中出现的内存带宽瓶颈给出了一种解决方案。十年前,我们用DDR SDRAM给出了一种相对RDRAM更经济的方案,使得内存位宽提升到128bit,但DDR内存的频率不可能永无止境地提高,所以此方法提高内存带宽将越来越困难。

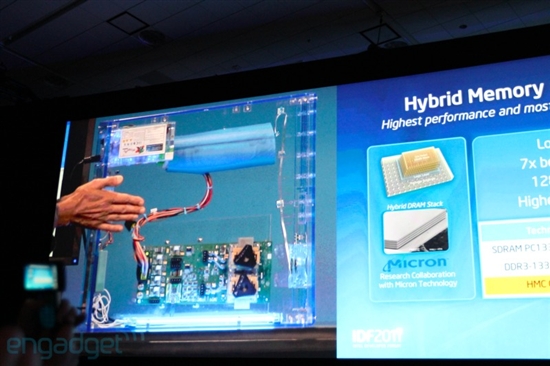

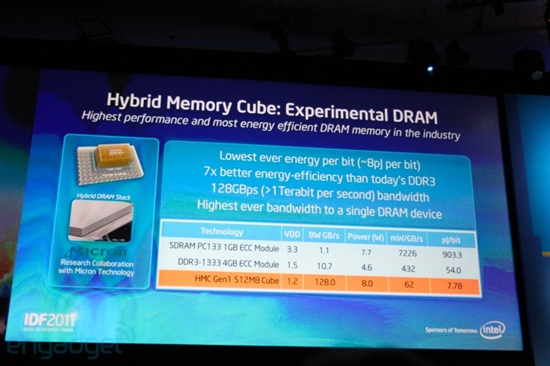

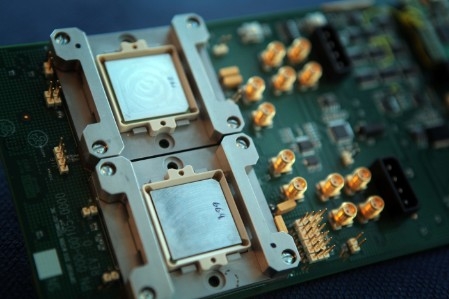

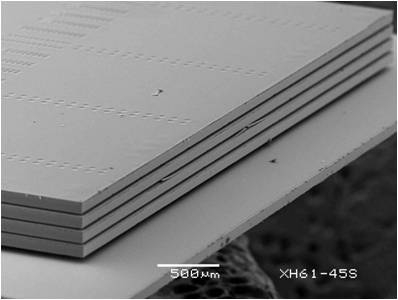

Intel和美光(Micron)的点子则是将多个DRAM芯片堆叠在一起,通过一个逻辑处理层(CPU处理意义上的,不是DRAM制造层面)用来做缓冲和路由,使得DRAM的总带宽得到极大提高,功耗几乎保持不变。此逻辑处理层是这种“夹心饼干”式内存的关键,解决了堆叠多层芯片一个很重要的问题:如何将针脚“连”至每层。这种逻辑路由层混合DRAM的技术自然得名为"Hybrid Memory Cube"。

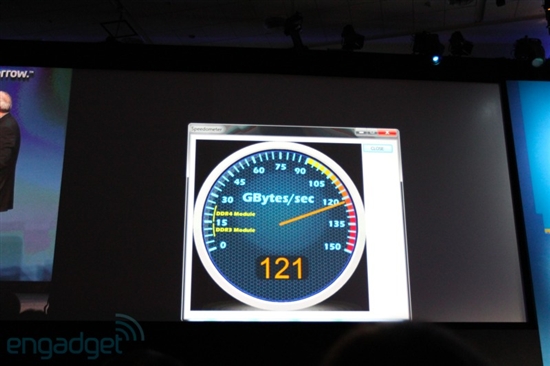

两家公司合作开发的HMC技术目前已经能做到和低电压DDR3对比,保持几乎相同能耗的情况下带宽达到1Tbit/s以上,效率是原来的7倍。但目前最大的问题是生产封装方面,不过相信业界真到有需要时自然会拿出解决办法。

本文收录在

#快讯

- 热门文章

- 换一波

- 好物推荐

- 换一波

- 关注我们

-

微博:快科技官方

快科技官方微博 -

今日头条:快科技

带来硬件软件、手机数码最快资讯! -

抖音:kkjcn

科技快讯、手机开箱、产品体验、应用推荐...