正文内容 评论(0)

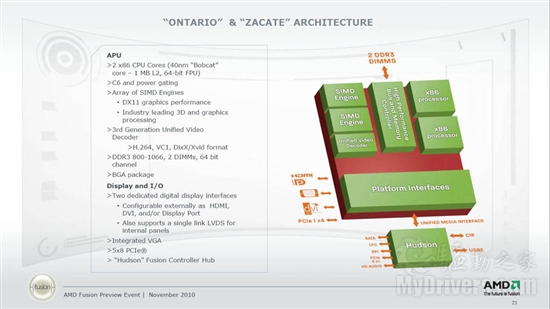

Zacate/Ontario APU的架构如出一辙,都有:

- 两个x86 CPU核心,山猫新架构,1MB二级缓存,64位浮点单元

- C6电源状态和电源栅极

- SIMD引擎阵列(GPU图形核心),支持DX11

- 第三代UVD视频解码器,支持H.264、VC-1、DivX/XviD

- 64位单通道DDR3-1066/800内存控制器,支持两组DIMM,电压1.35/1.5V

- BGA封装

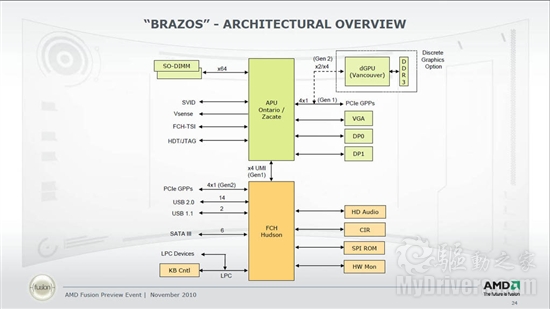

这就是Brazos平台的架构图,包括Zacate/Ontario APU、Hudson FCH两大部分,后者也是单芯片设计,详细规格后边会有介绍。

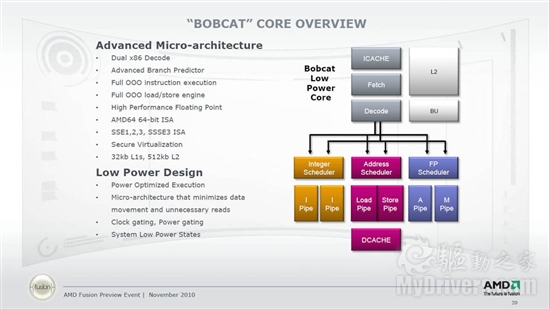

山猫架构是Zacate/Ontario APU之中CPU部分的基础。从微架构方面看,其主要特点有双x86解码器、高级分支预测器、完整乱序执行指令执行、完整乱序执行载入和存储引擎、高性能浮点单元、AMD64 64位ISA指令集、SSE1/2/3/SSSE3 ISA指令集、安全虚拟化、每核心32KB一级缓存和512KB二级缓存,而且它特别采用了低功耗设计理念,包括功耗优化执行、数据移动和非必要读取最小化、时钟栅极和电源栅极、系统低功耗状态等等。

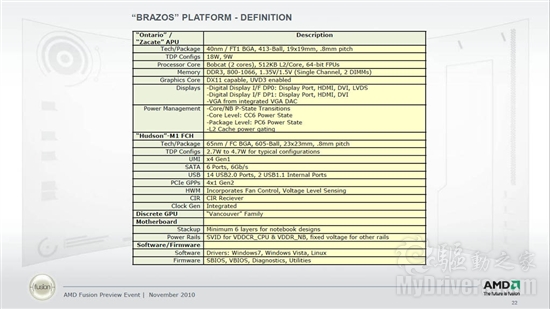

Zacate/Ontario APU采用台积电40nm工艺制造,FT1 BGA 413-Ball封装,封装面积19×19毫米,核心面积75平方毫米,显示输出支持LVDS、VGA、DVI、HDMI、DisplayPort等不同组合,电源管理技术包括核心与北桥P状态转换、核心级CC6电源状态、封装级PC6电源状态、二级缓存电源栅极。

Hudson M1 PCH控制芯片则是65nm工艺制造,FC BGA 605-Ball封装,封装面积23×23毫米,热设计功耗2.7-4.7W,通过PCI-E 1.1 x4 UMI总线与APU相连,支持六个SATA 6Gbps、十四个USB 2.0、两个USB 1.1接口,集成四条PCI-E 2.0 x1 GPP通道、风扇控制和电压级别传感硬件监控、CIR红外接收器、时钟发生器。

AMD还对主板设计提出了要求,比如PCB至少六层,供电也要满足一定的标准。

这就是Zacate APU芯片实物的正反面。

本文收录在

#快讯

- 热门文章

- 换一波

- 好物推荐

- 换一波

- 关注我们

-

微博:快科技官方

快科技官方微博 -

今日头条:快科技

带来硬件软件、手机数码最快资讯! -

抖音:kkjcn

科技快讯、手机开箱、产品体验、应用推荐...