正文内容 评论(0)

旧金山秋季IDF 2010:昨天,Intel对下代处理器架构Sandy Bridge(官方简称SNB)的一些技术特点做了深入阐述,并展示了美丽的晶圆和芯片照片。今天,我们就深入新架构内部,看看它到底有哪些神奇的地方。喜欢钻研技术的硬件玩家们,饕餮盛宴来了。

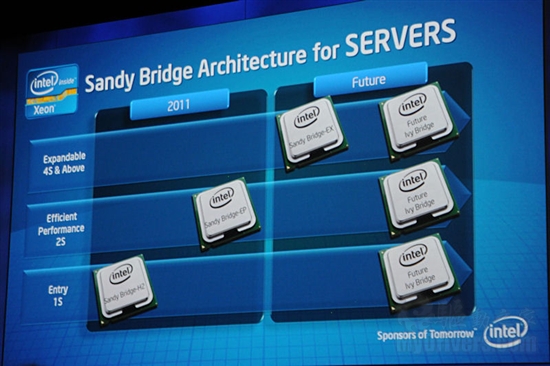

SNB是Intel 2011年的一次重大架构更新,官方称为“2011年第二代Intel Core处理器家族”,主要针对性能级和主流市场,而高端领域暂时继续交给Gulftown Core i7-900系列六核心,入门级领域则要到明年底甚至2012年才会升级。

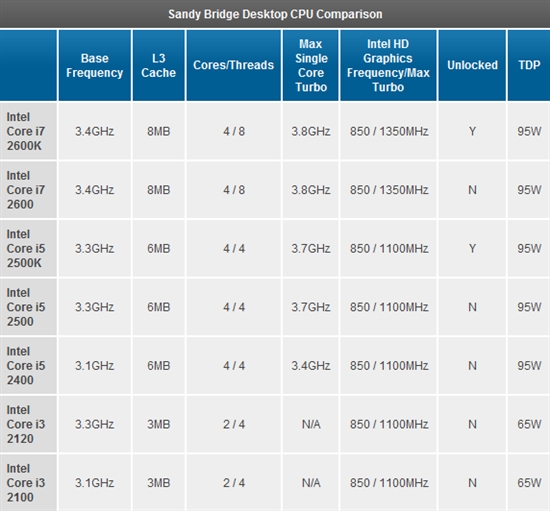

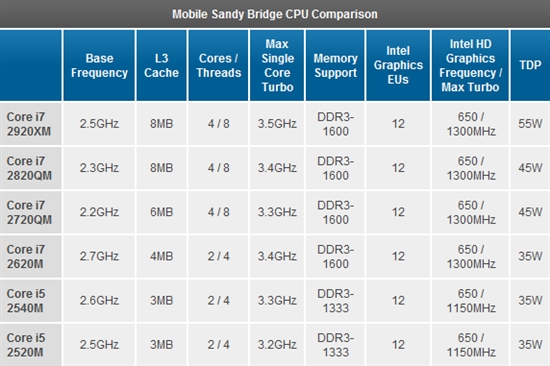

SNB首批产品将于2011年初发布并上市,同时涵盖桌面和笔记本,架构方面也基本相同,具体型号和规格如下:

从左至右:Nehalem、Westmere、Sandy Bridge(上方是一颗SNB处理器)

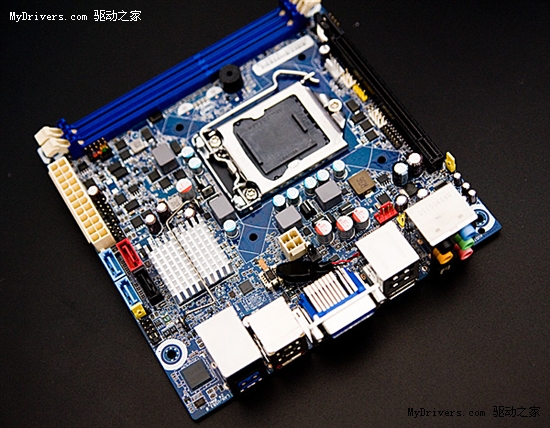

除了处理器,配套的芯片组、主板、散热器等也会一并更新,其中芯片组是6系列,桌面上主要有P67、H67、H61等型号,原生支持最多两个SATA 6Gbps接口,但没有原生USB 3.0,仍需要依赖第三方控制器,另外还有PCI-E 2.0 5GT/s高速总线。

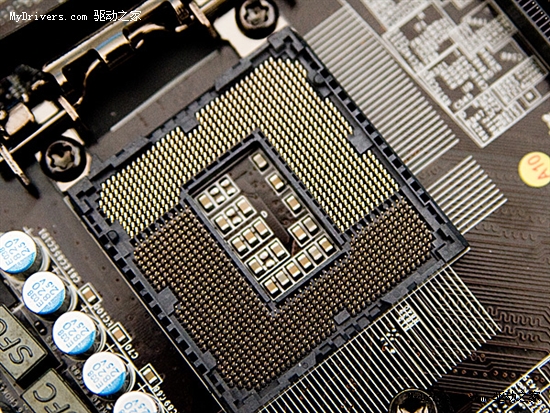

6系列主板的插座将改为LGA1155,不兼容当前的LGA1156。

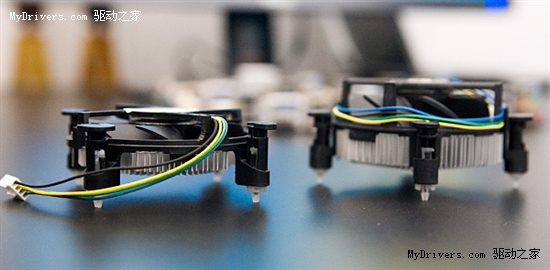

原装散热器也随着处理器功耗的降低而瘦身,特别是45W低功耗版本会搭配半高式矮版散热器。

一、前端

从高级层面角度看,SNB架构只是一次进化,但是如果看看Nehalem/Westmere以来晶体管变化的规模,绝对是一次革命。

Core 2引入了一种叫作循环流检测器(LSD)的逻辑块,检测到CPU执行软件循环的时候就会关闭分支预测器、预取/解码引擎,然后通过自身缓存的微指令(micro-ops)供给执行单元。这种做法通过在循环执行的时候关闭前端节省了功耗,并改进了性能。

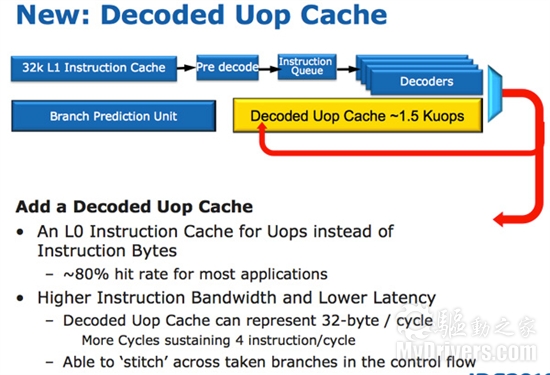

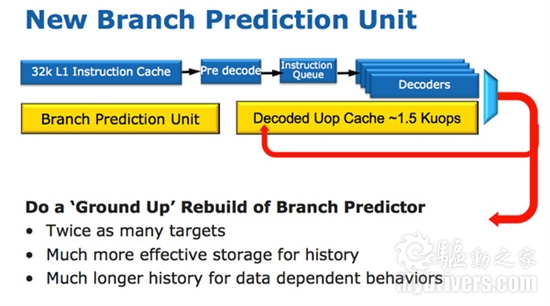

SNB里又增加了一个微指令缓存,用于在指令解码时临时存放。这里没有什么严格的算法,指令只要在解码就会放入缓存。预取硬件获得一个新指令的时候,会首先检查它是否存在于微指令缓存中,如是则由缓存为其余的管线服务,前端随之关闭。解码硬件是x86管线里非常复杂的部分,关闭它能够节约大量的功耗。如果这种技术也能引入到Atom处理器架构中,无疑也能使之受益匪浅。

这个缓存是直接映射的,能存储大约1.5K微指令,相当于6KB指令缓存。它位于一级指令缓存内,大多数程序的命中率都能达到80%左右,而且带宽也相比一级指令缓存更高、更稳定。真正的一级指令和数据缓存并没有变,仍然都是32KB,合计64KB。

这看起来有点儿像Pentium 4的追踪缓存,但最大的不同是它并不缓存追踪,而更像是一个指令缓存,存储的是微指令,而非x86指令(macro-ops)。

与此同时,Intel还完全重新了一个分支预测单元(BPU),精确度更高,并在三个方面进行了创新。

第一,标准的BPU都是2-bit预测器,每个分支都使用相关可信度(强/弱)进行标记。Intel发现,这种双模预测器所预测的分支几乎都是强可信度的,因此SNB里多个分支都使用一个可信度位,而不是每个分支对应一个可信度位,结果就是在分支历史表中同样的位可以对应更多分支,进而提高预测精确度。

第二,分支目标同样做了翻新。之前的架构中分支目标的大小都是固定的,但是大多数目标都是相对近似的。SNB现在支持多个不同的分支目标大小,而不是一味扩大寻址能力、保存所有分支目标,因而浪费的空间更少,CPU能够跟踪更多目标、加快预测速度。

第三,提高分支预测器精度的传统方法是使用更多的历史位,但这只对要求长指令的特定类型分支有效,SNB于是将分支按照长短不同历史进行划分,从而提高预测精度。

二、物理寄存器文件(PRF)和执行改进

类似于AMD的推土机、山猫,Intel SNB也使用了物理寄存器文件。Core 2、Nehalem架构中,每个微指令需要的每个操作数都有一份拷贝,这就意味着乱序执行硬件(调度器/重排序缓存/关联队列)必须要非常大,以便容纳微指令和相关数据。Core Duo时代是80-bit,加入SSE指令集后增至128-bit,现在又有了AVX指令集,按照趋势会翻番至256-bit。

RPF在寄存器文件中存储微指令操作数,而微指令在乱序执行引擎中只会携带指向操作数的指针,而非数据本身。这就大大降低了乱序执行硬件的功耗(转移大量数据很费电的),同时也减小了流水线的核心面积,数据流窗口也增大了三分之一。

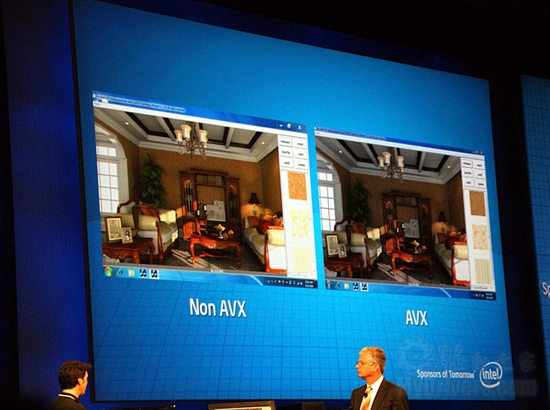

核心面积的精简正是AVX指令(SNB最主要革新之一)集得以实现并保证良好性能的关键所在。以最小的核心面积代价,Intel将所有SIMD单元都转向了256-bit。

AVX支持256-bit操作数,相当消耗晶体管与核心面积,而RPF的使用加大了乱序执行缓冲,能够很好地满足更高吞吐量的浮点引擎。

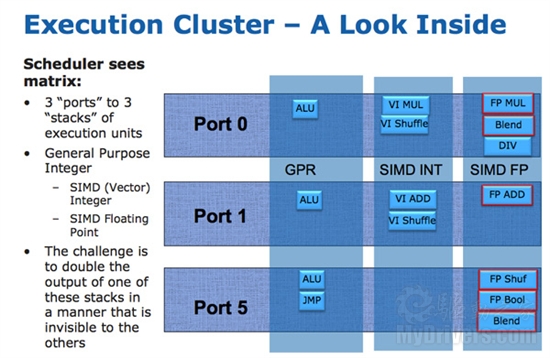

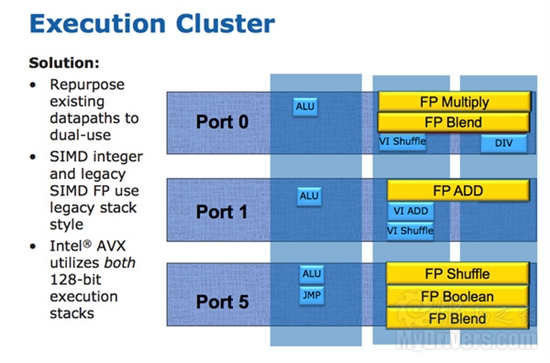

Nehalem架构中有三个执行端口和三个执行单元堆栈:

SNB允许256-bit AVX指令借用128-bit的整数SIMD数据路径,这就使用最小的核心面积实现了双倍的浮点吞吐量,每个时钟可以进行两个256-bit AVX操作。另外执行硬件和路径的上位128-bit是受电源栅极(Power Gate)控制的,标准128-bit SSE操作不会因为256-bit扩展而增加功耗。

AMD推土机架构对AVX的支持则有所不同,使用了两个128-bit SSE路径来合并成256-bit AVX操作,即使八核心(四模块)推土机的256-bit AVX吞吐量也要比四核心SNB少一半,不过实际影响完全取决于应用程序如何利用AVX。

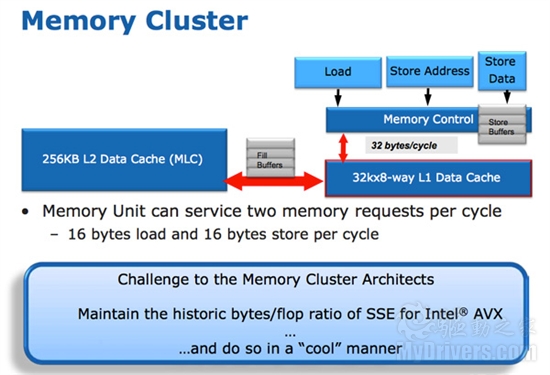

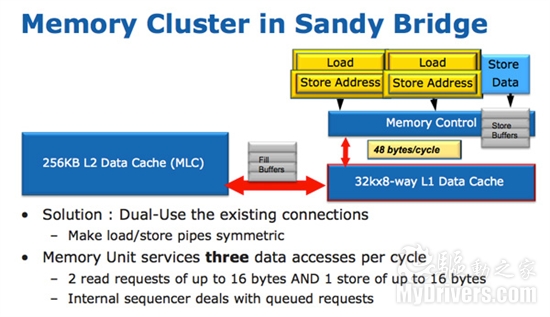

SNB的峰值浮点性能翻了一番,这就对载入和存储单元提出了更高要求。Nehalem/Westmere架构中有三个载入和存储端口:载入、存储地址、存储数据。

SNB架构中载入和存储地址端口是对称的,都可以执行载入或者存储地址,载入带宽因此翻倍。

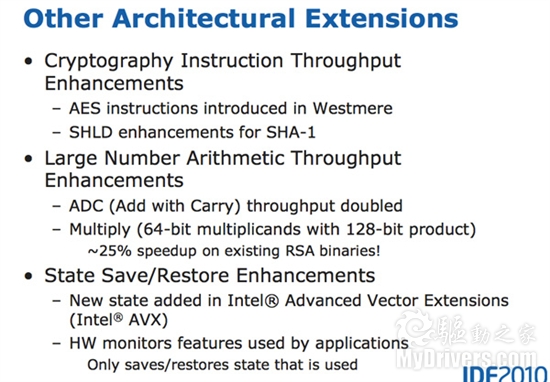

SNB的整数执行也有了改进,只是比较有限。ADC指令吞吐量翻番,乘法运算可加速25%。

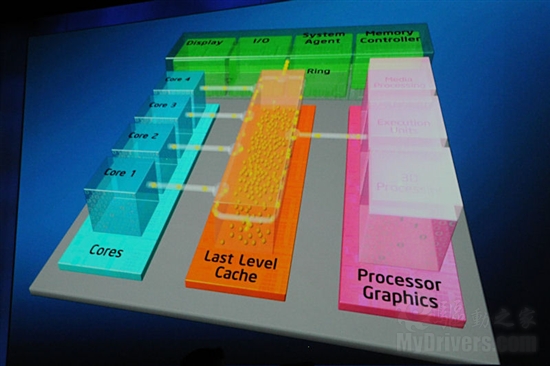

三、环形总线与三级缓存

Nehalem/Westmere每个核心都与三级缓存单独相连,都需要大约1000条连线,而这种做法的缺点是如果频繁访问三级缓存,效果可能不会太好。

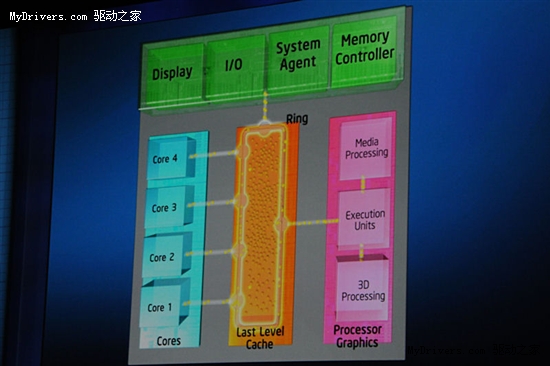

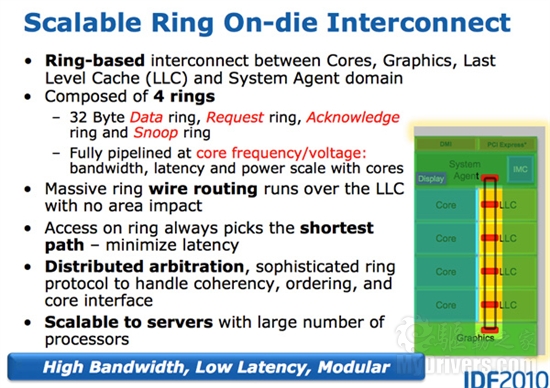

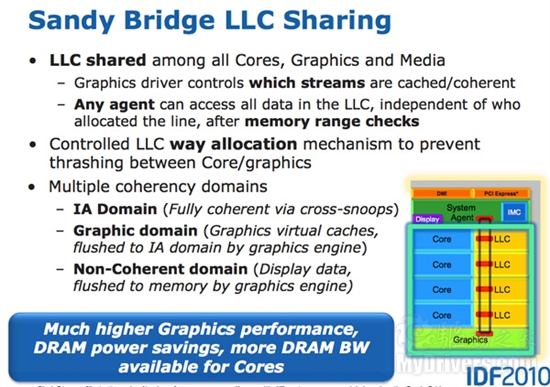

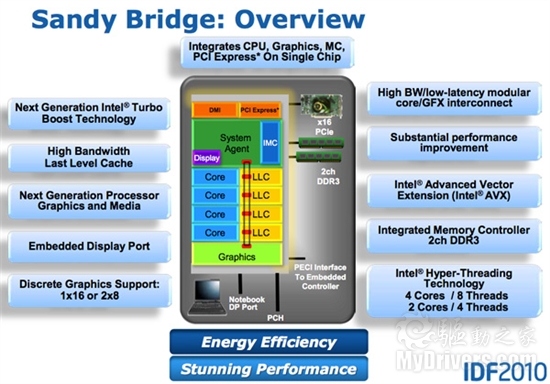

SNB又整合了GPU图形核心、视频转码引擎,并共享三级缓存。Intel并没有沿用此前的做法,再增加2000条连线,而是像服务器版的Nehalem-EX、Westmere-EX那样,引入了环形总线(Ring Bus),每个核心、每一块三级缓存(LLC)、集成图形核心、媒体引擎、系统助手(System Agent)都在这条线上拥有自己的接入点,形象地说就是个“站台”。

这条环形总线由四条独立的环组成,分别是数据环(DT)、请求环(QT)、响应环(RSP)、侦听环(SNP)。每条环的每个站台在每个时钟周期内都能接受32字节数据,而且环的访问总会自动选择最短的路径,以缩短延迟。随着核心数量、缓存容量的增多,缓存带宽也随时同步增加,因而能够很好地扩展到更多核心、更大服务器集群。

这样,SNB每个核心的三级缓存带宽都是96GB/s,堪比高端Westmere,而四核心系统更是能达到384GB/s,因为每个核心都在环上有一个接入点。

三级缓存的延迟也从大约36个周期减少到26-31个周期。此前预览的时候我们就已经感觉到了这一点,现在终于有了确切的数字。三级缓存现在被划分成多个区块,分别对应一个CPU核心,都在环形总线上有自己的接入点和完整缓存管线。每个核心都可以访问全部三级缓存,只是延迟不同。此前三级缓存只有一条缓存管线,所有核心的请求都必须通过它,现在很大程度上分而治之了。

和以前不同的是,三级缓存的频率现在也和核心频率同步,因而速度更快,不过缺点是三级缓存也会随着核心而降频,所以如果CPU降频的时候GPU又正好需要访问三级缓存,速度就慢下来了。

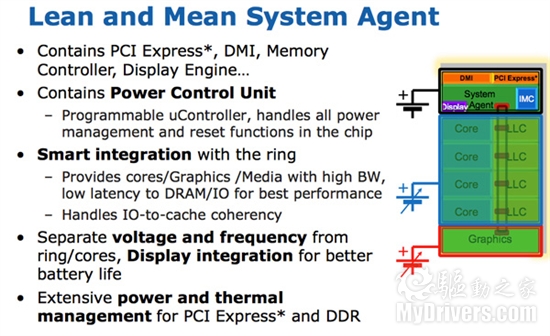

四、系统助手

经过环形总线、三级缓存的变化,非核心(Uncore)概念还在,但是Intel改称之为系统助手,基本就相当于曾经的北桥芯片:

PCI-E控制器,可提供16条PCI-E 2.0信道,支持单条PCI-E x16或者两条PCI-E x8插槽;

重新设计的双通道DDR3内存控制器,内存延迟也恢复了正常水平(Westmere将内存控制器移出CPU、放到了GPU上);

此外还有DMI总线接口、显示引擎、电源控制单元(PCU)。

系统助手的频率要低于其他部分,有自己独立的电源层。

五、整合图形核心

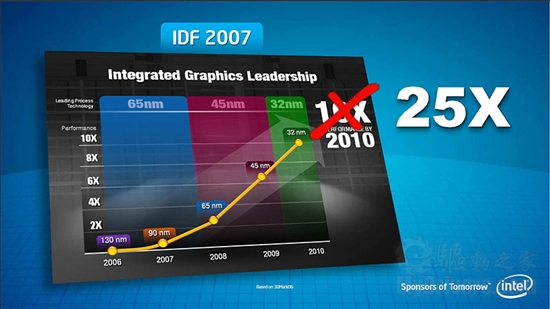

Intel的集成显卡似乎总是个笑话,但这次确实不一样了。SNB的CPU性能相比现在提升了10-30%,进化到第六代的GPU图形性能则会轻松翻好几番。

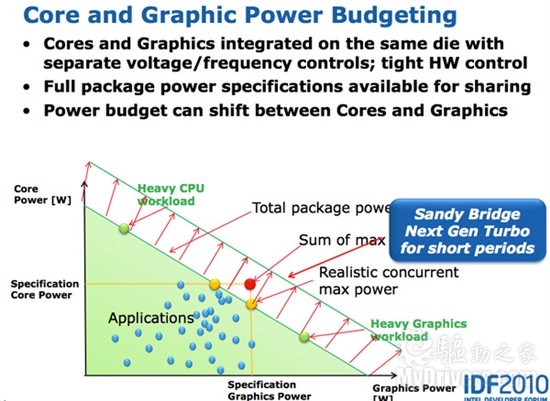

Westmere虽然也自带了图形核心,但与CPU是双内核封装,只是通过45nm工艺、更多着色硬件、更高频率提升了性能,SNB则将CPU、GPU封装在同一内核中,全部采用32nm工艺,特别是显著提高了IPC(指令/时钟)。

SNB GPU有自己的电源岛和时钟域,也支持Turbo Boost技术,可以独立加速或降频,并共享三级缓存。显卡驱动会控制访问三级缓存的权限,甚至可以限制GPU使用多少缓存。将图形数据放在缓存里就不用绕道去遥远而“缓慢”的内存了,这对提升性能、降低功耗都大有裨益。

不过这么做并没有说起来这么简单。NVIDIA GF100核心费了九牛二虎之力,SNB其实也差不多,同样进行了全新设计。

顺便提一下Intel的独立显卡工程Larrabee。它的重点是广泛使用全面可编程硬件(除了纹理硬件),SNB则是全面使用固定功能硬件,功能特性和硬件单元相对应,这样的好处是性能、功耗、核心面积都大大优化,损失则是缺乏弹性。显然,Intel世界的中心仍旧是CPU,不能让GPU过分强大,这和NVIDIA的理念正好相反。

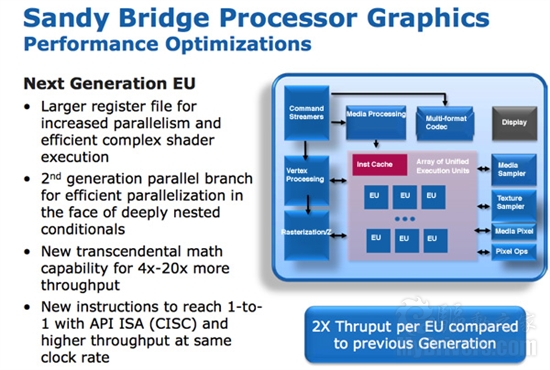

可编程着色硬件被称为EU,包含着色器、核心、执行单元等,可以从多个线程双发射时取指令。内部ISA映射和绝大多数DX10 API指令一一对应,架构很像CISC,结果就是有效扩大了EU的宽度,IPC也显著提升。

抽象数学运算由EU内的硬件负责,性能得以同步提高。Intel表示,正弦(sine)、余弦(cosine)操作的速度比现在的HD Graphics提升了几个数量级。

Intel此前的图形架构中,寄存器文件都是即时重新分配的。如果一个线程需要的寄存器较少,剩余寄存器就会分配给其他线程。这样虽能节省核心面积,但也会限制性能,很多时候线程可能会面临没有寄存器可用的尴尬。在芯片组集成时代,每个线程平均64个寄存器,Westmere HD Graphics提高到平均80个,SNB则每个线程固定为120个。

所有这些改进加起来,SNB里每个EU的指令吞吐量都比现在的HD Graphics增加了一倍。

SNB集成的GPU图形核心分为两大版本,分别拥有6个、12个EU。首批发布的移动版全部是12个EU,桌面版则根据型号不同而有两种配置,可能是高端12个、低端6个。得益于每个EU吞吐量翻番、运行频率更高、共享三级缓存等特点,即使只有六个的时候性能也会相当令人满意。

下边就是移动版SNB、GeForce 310M同时运行《星际争霸2》:

六、媒体引擎

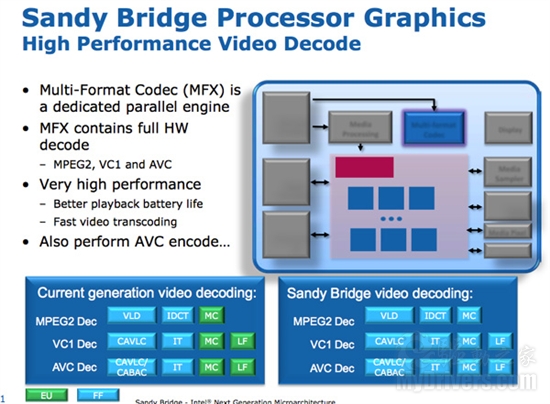

除了GPU图形核心,SNB中还有一个媒体处理器,专门负责视频解码、编码。

新的硬件加速解码引擎中,整个视频管线都通过固定功能单元进行解码,和现在正好相反。Intel据此宣称,SNB在播放视频的时候功耗可降低一半。

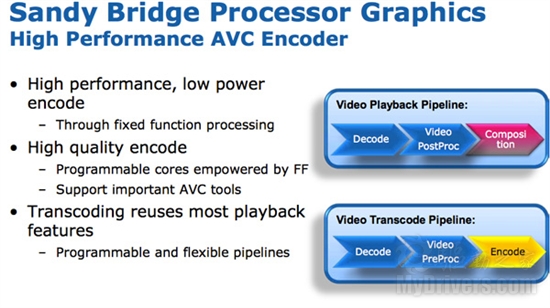

视频编码引擎则是全新的。具体细节没有公布,但是Intel现场拿出了一段3分钟长的1080p 30Mbps高清视频,将其转换成640×360 iPhone格式,结果整个过程耗时仅仅14秒钟,转换速度高达400FPS左右,而这只花费了大约3平方毫米的核心面积。

Intel与软件产业合作密切,相信这种视频转码技术会很快得到广泛支持。

七、新一代Turbo Boost

Lynnfield Core i7/i5首次引入了智能动态加速技术“Turbo Boost”(睿频),能够根据工作负载,自动以适当速度开启全部核心,或者关闭部分限制核心、提高剩余核心的速度,比如一颗热设计功耗(TDP)为95W的四核心处理器,可能会三个核心完全关闭,最后一个大幅提速,一直达到95W TDP的限制。

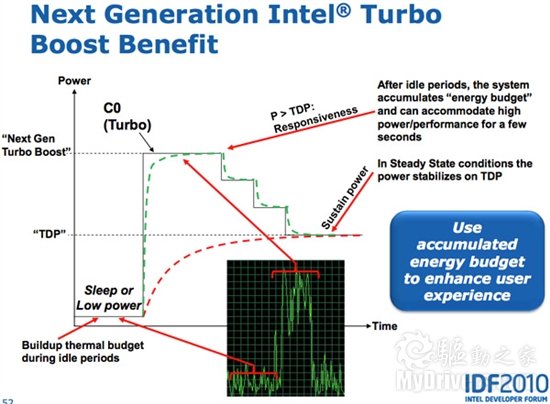

现有处理器都是假设一旦开启动态加速,就会达到TDP限制,但事实上并非如此,处理器不会立即变得很热,而是有一段时间发热量距离TDP还差很多。

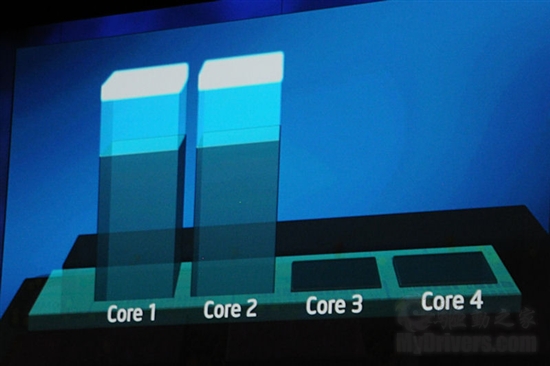

SNB利用这一点特性,允许单元控制单元(PCU)在短时间内将活跃核心加速到TDP以上,然后慢慢降下来。PCU会在空闲时跟踪散热剩余空间,在系统负载加大时予以利用。处理器空闲的时间越长,能够超越TDP的时间就越长,但最长不超过25秒钟。

不过在稳定性方面,PCU不会允许超过任何限制。

之前我们也已经说过了,SNB GPU图形核心也可以独立动态加速,最高可达惊人的1.35GHz。如果软件需要更多CPU资源,那么CPU就会加速、GPU同时减速,反之亦然。

结语:

出于各种原因,硬件厂商在新产品发布之前都不愿意公开太多架构方面的资料,性能数据更是不允许(所以之前的预览被删了),但是这一次,SNB发布还有四个多月,我们已经能够比较详尽地了解新架构的种种特性了。

虽然SNB并不像Intel宣称的那样是一个全新架构,严格来说只是现有架构的改进和增强,本质并没有变,但很多模块也进行了彻底重新设计,细节之处的优化和增强也大大提高了执行效率,SNB在功能特性、性能、功耗等各方面的表现无疑都会更加出色。

改进的动态加速技术同样令人兴奋。它意味着我们可以在不同情况下都能很好地释放多核心、高频率处理器的潜力,既不会造成资源浪费,也不会面临性能紧缺,并能很好地协调CPU、GPU资源。

更重大的变化还在于CPU核心之外,也即是集成的图形核心与媒体引擎。GPU性能绝对是SNB的一大亮点,Intel集成显卡也终于有望甩掉低能的帽子。假设如果能够维持很好的画质,并得到软件的广泛支持,视频转码也将是一项杀手级新特性,提速10倍的表现想不吸引人都难,NVIDIA CUDA、AMD Stream也会感受到很大威胁。

环形总线也是SNB的一大突破,这种底层架构变化并不多见。看起来很有扩展性,能够支持不断增长的核心数量、三级缓存容量、GPU性能,也有望将多核心时代变成众核心时代。

本文收录在

#快讯

- 热门文章

- 换一波

- 好物推荐

- 换一波

- 关注我们

-

微博:快科技官方

快科技官方微博 -

今日头条:快科技

带来硬件软件、手机数码最快资讯! -

抖音:kkjcn

科技快讯、手机开箱、产品体验、应用推荐...