正文内容 评论(0)

问:SCC中每两个核心组成的Tile可以运行在自己的频率上,内存控制器也有不同的频率,但整个网格网络看起来却是统一频率。未来芯片是否也会这样不同的部分有着不同的内部频率?

答:我不是产品事业部的,所以不能对实际产品发表评论,但是我们创造了这种试验芯片,所以如果微处理器永远停留在同样的时钟频率上,我肯定会很吃惊。作为研究人员,我个人同意你的说法。当然停留在同样的频率上也有好处,比如说控制功率门限。除了频率不同之外也有其他选择,比如降低芯片某些部分的速度,甚至在特定始终循环里彻底关闭某一部分。我想我们会看到芯片的不同部分根据任务需要运行在不同性能点上。

问:AMD Llano之类的异构多核心理念是不是会更好一些?

答:异构处理是最理想的方案,但也有一些需要注意的地方,比如应用负载均衡、标量处理,矢量处理也是很复杂、低效的。只有在应用程序内通过指令集才能实现。如果操作系统或者常驻内核能够分析应用程序的需要,将负载导向何时的处理器(矢量、标量、矩阵等等),集成异构处理器的效率将是惊人的。

硬件正在拉大相对于软件的领先地位。二十世纪八十年代,硬件的效率无法满足软件;九十年代初,硬件和软件基本持平;新千年里,硬件能力每隔一年就能超过软件需要大约六个月。软件开发还没有自己的摩尔定律。

问:您如何看待AMD Fusion理念?它是否会成功?

答:它不仅会成功,也是不必避免、必不可少的。它对物理分离的标量和矢量处理器来说效率不足(综合起来就高效了)。通过三级缓存进行处理器内部通信的优势非常明显,不容忽视。还有新的制造工艺。打造这种超级复杂的系统是经济可行的。

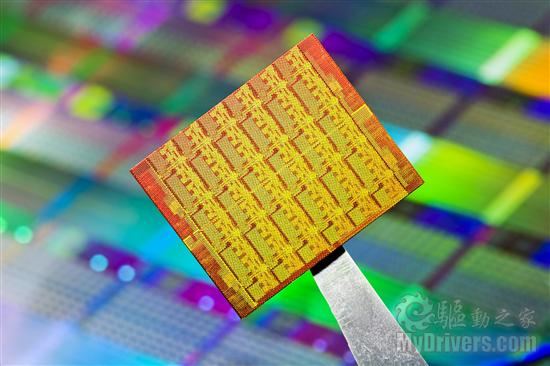

问:你们是如何将48个核心放在一起并保持125W热设计功耗的?这太牛了。

答:我们有能力很好地管理功耗,比如不同的电压和频率分区,同时我们也在设计方面做出了一些牺牲(比如前边提到的缺乏矢量浮点单元和二级缓存一致性)。

问:关于SCC集成的高效四通道DDR3内存控制器有没有更多信息可以透露?它和目前使用的内存控制器有何不同?

答:SCC里的内存控制器是根据不同操作点进行优化的。每个内存控制器需要配合12个核心,就并行机制而言是相当多的,因此它针对更好地管理大量单线程进行了优化,而不是少量多线程。它针对更高并行度的访问进行了优化,而传统内存控制器更适合有限数量线程情况下的性能。

问:那么这代表着内存控制器的未来?

答:它是一种适合多核心架构的内存控制器,也能很好地用于大核心。

问:在SCC项目上,软件开发产业有什么责任?这种系统是否已向软件厂商出货?

答:我们已经开始和特定的外部合作伙伴分享这种系统。目前已经取得了一些很有趣的成果,而且我想今年夏天还会有更有趣的消息。这些机构才应该对他们的成果发表评论。

本文收录在

#快讯

- 热门文章

- 换一波

- 好物推荐

- 换一波

- 关注我们

-

微博:快科技官方

快科技官方微博 -

今日头条:快科技

带来硬件软件、手机数码最快资讯! -

抖音:kkjcn

科技快讯、手机开箱、产品体验、应用推荐...