正文内容 评论(0)

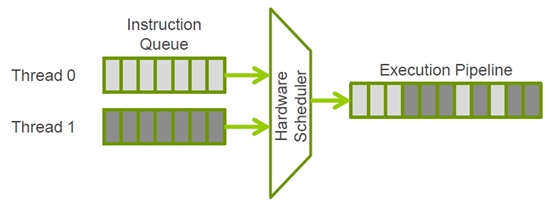

interAptiv产品家族最大的特点是支持超线程——目前ARM还没有一款产品引入超线程技术。随着采用Intel Medfield Atom产品的智能设备上市,引入超线程技术对于目前日常使用的负载下性能的提升可谓非常有利。

MIPS称3个interAptiv核心的性能表现类似或略微超过2个Cortex-A9/3个Cortex-A5核心,核心面积综合三者也大致相当。当然MIPS着重宣传的CoreMark测试分数interAptiv肯定占优势。而interAptiv家族产品中CPU执行管线为多个线程所共享,可减轻内存访问延迟对于性能的冲击程度。

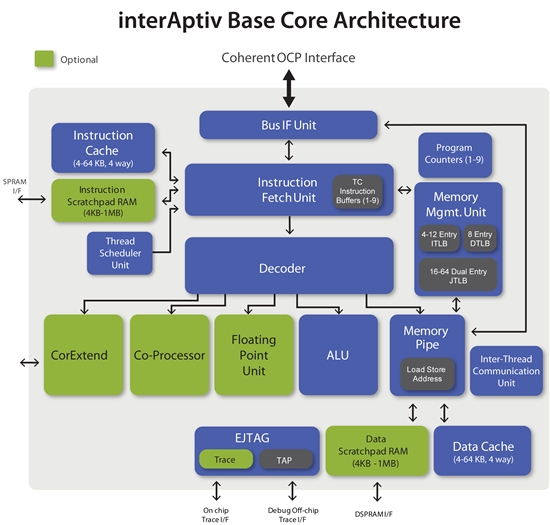

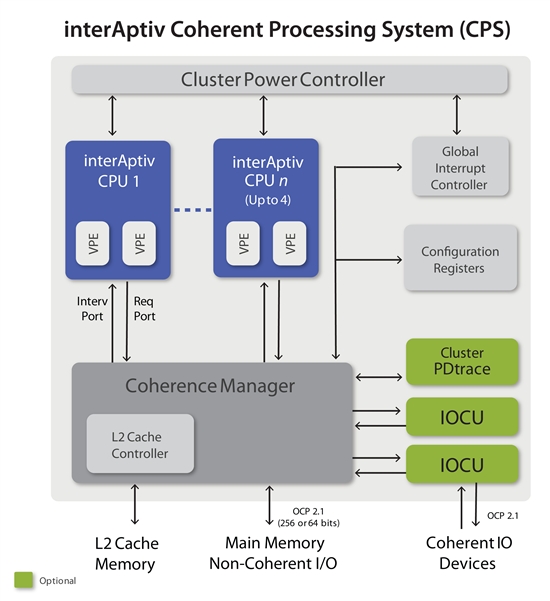

MIPS将进程解释为VPE(Virtual Processing Elements),interAptiv核心的流水线深度为9级,不支持乱序执行。而支持多线程的IEEE 754标准FPU为可选项,具体厂商/用户可根据自己需求定制。此外DSP ASE多媒体处理引擎以及EVA扩展寻址技术也同样为可选模块。节能技术部分interAptiv和proAptiv同样应用CPS系统。但与proAptiv对比,interAptiv核心架构的节能技术更进一步,核心可以在低负载下完全关闭:频率降为0并且L1指令+数据缓存可在此时智能选择,而proAptiv只能智能选择L1指令缓存。

如使用台积电40nm G工艺制造,interAptiv产品家族最高频率可达1GHz并附带一切模块和超线程功能,如放弃超线程功能中的硬件调度部分频率可达1.2GHz,最后如果去掉多媒体处理引擎频率可冲至1.5GHz。MIPS表示这些参考值为“甜点”频率,此时功耗比处于最佳状态。当然这仅仅是授权标准,实际产品如何取舍由用户自行选择。

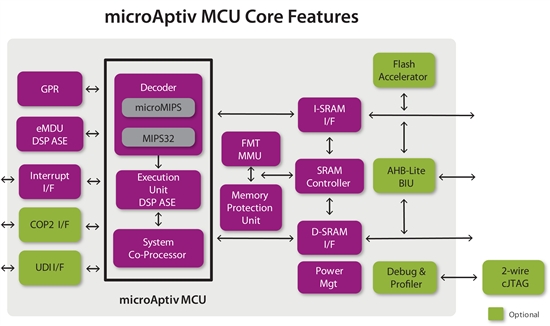

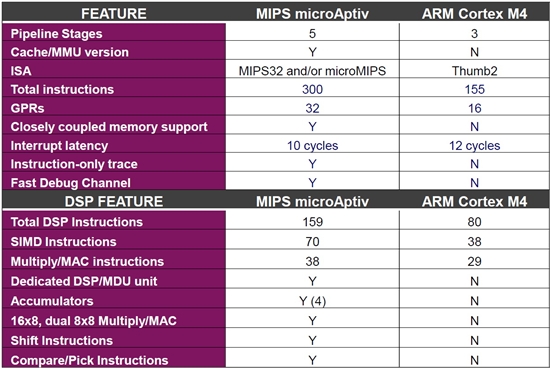

而应用于工业微控制领域最底端的microAptiv系列产品为此前M14k/c的“软件优化”版,支持microMIPS代码压缩。由于整合了DSP ASE引擎,信号处理可在更低成本下完成。

这种5级流水线的架构核心频率在65nm LP制程下最高可达400MHz,MIPS同时给出了和Cortex-M4的对比:

当然,对比Cortex-M4多出来一堆特性面积上肯定也要更大:在90nm LP制程工艺的条件下,ARM给出的数据是Cortex-M4的面积为0.17平方毫米,而无缓存版microAptiv MCU的面积为0.42平方毫米。但MIPS对Anandtech称上述数据非同条件对比,在90nm LP工艺面积优化过后microAptiv只比Cortex-M4面积大0.01平方毫米。总之这点公说公有理婆说婆有理,不管大多少反正只要有附加特性肯定得用多余的面积来换。

本文收录在

#CPU处理器

- 热门文章

- 换一波

- 好物推荐

- 换一波

- 关注我们

-

微博:快科技官方

快科技官方微博 -

今日头条:快科技

带来硬件软件、手机数码最快资讯! -

抖音:kkjcn

科技快讯、手机开箱、产品体验、应用推荐...