正文内容 评论(0)

除了介绍Xeon E5系列,Intel今天还首次展示了基于众核心(MIC)架构的新型协处理器“Knights Corner”,根据DGEMM测试其双精度浮点性能已经超过一万亿次每秒(1TFlops),这也是历史上第一次做到这一点的处理器芯片。

相比之下,目前最强大的专用并行加速器是NVIDIA Tesla M2090,双精度浮点峰值性能665GFlops(6650亿次每秒),大大低于Intel KNC。

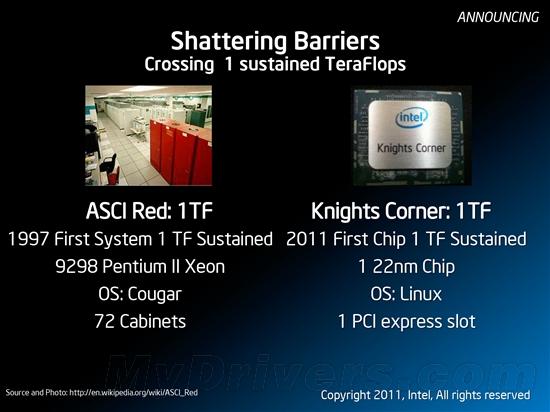

回首1997年,Intel曾经利用9298颗Pentium II Xeon处理器打造了第一台计算性能突破TFlops大关的超级计算机“ASCI Red”,整套系统占据72个机柜,而KNC只需要一个PCI-E扩展插槽就可以了。

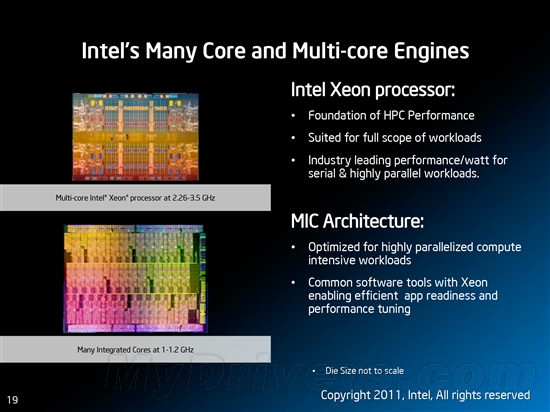

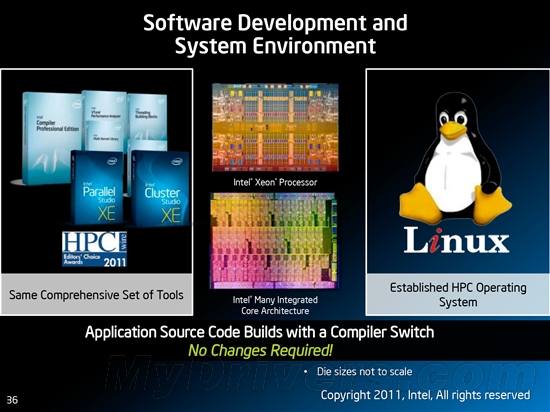

KNC协处理器将是第一款投入商用的MIC架构产品,计划采用22nm Tri-Gate工艺制造,核心数量超过50个,频率1.0-1.2GHz。通过搭配同步推出的Xeon E5系列,KNC既可以利用专为高度并行负载设计的新架构提供超高性能,又可以兼容现有的x86编程模型和工具。

按照Intel的设想,Xeon E5系列是高性能计算的基础,MIC架构芯片则专门执行高度并行的计算密集型任务,二者相辅相成。

德克萨斯高级计算中心已经联合戴尔,率先部署了一套拥有八个Xeon节点、八个MIC节点的试验集群,十月份投入运行,主要用于生物化学、天体物理学、计算流体动力学等方面的研究,嗨计划在2013年一月建成类似结构的新系统“Stampede”,性能超过10PFlops。

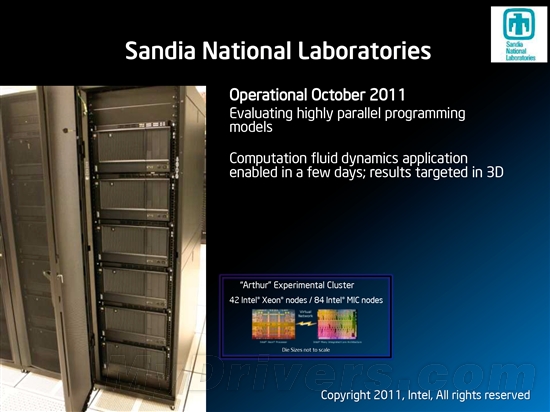

桑迪亚国家实验室也在十月份建成了一套42个Xeon节点、84个MIC节点的试验系统,评估高度并行编程模型,可在数天内完成计算流体动力学任务。

此外,Intel曾在汉堡举办的2011国际超级计算会议上宣布要在2018年实现百亿亿级(Exascale)性能、且功耗仅比现有顶级高性能计算系统增加一倍的目标。今天,Rajeeb Hazra就公布了几项新计划以帮助实现这一目标。

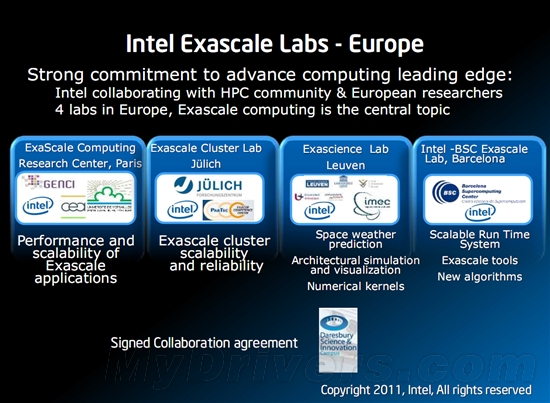

Intel和巴塞罗那超级计算中心(BSC)签订了一份长期协议,旨在与该中心合作,在巴塞罗那建立百亿亿级实验室。这将是继法国巴黎、德国尤利西(Juelich)和比利时鲁汶(Lueven)的实验室之后,Intel在欧洲成立的第四个百亿亿级研发实验室,而它将专注于编程中的可扩展性问题以及百亿亿级高性能计算系统的运行时系统。

此外,英国科学和技术设施委员会(STFC)也与Intel签署了一份备忘录,旨在共同开发和测试未来高性能计算机所需的技术。

本文收录在

#快讯

- 热门文章

- 换一波

- 好物推荐

- 换一波

- 关注我们

-

微博:快科技官方

快科技官方微博 -

今日头条:快科技

带来硬件软件、手机数码最快资讯! -

抖音:kkjcn

科技快讯、手机开箱、产品体验、应用推荐...