正文内容 评论(0)

AMD FX系列处理器空有八个核心和3.6GHz高频率,但实际性能却令人无法满意,难道只能归咎于新架构的不适应么?多年前已经离开AMD的工程师Cliff A. Maier站出来评论说,这其实要归咎于AMD在推土机上采取的设计方式是错误的,不再手工打造、精心调教而过于依赖自动设计软件,结果虽然加快了研发进度(相对而言),却无法提供最高性能与效率。

Cliff A. Maier在网上发帖称:“从设计图上,推土机是一款非常漂亮的芯片……(但是)管理团队决定应该进行交叉工程(cross-engineering),这就意味着我们不得不放弃手工打造我们的处理器设计,改而转向SoC设计方式,结果就是牺牲了很多性能、芯片面积和效率。DEC Alphas之所以速度飞快,原因就在于它的每个晶体管都是手工设计的。Intel、AMD至少在芯片的关键部位上也是一向如此。在我离开之前,一切都变了。他们开始依赖合成工具、自动布局和路由工具。”

这位老工程师曝料称:“离职前我长期负责设计流程的管理,也曾经测试过这些工具。我让那些推销这类设计工具的公司用它们进行试验,时间不做任何限制,结果最终给我的设计总是比我们的手工设计要大上20%,速度也慢20%,而且还有电子迁移等一系列问题。这就是AMD现在设计芯片的方式,我相信会表现很好的。”

Cliff A. Maier继续评论说:“至少有一件事是可以肯定的。AMD应该借鉴K8以及K8团队的成功经验、设计理念,而不是用一帮从未有任何成就的人去做一个项目,却最终将其取消。Intel花了很多年才搞出来Nehalem,AMD还差得远。他们银行里可可没有那么多钱,不然也不会轻易在反垄断问题上与Intel妥协,更不会卖掉自己的工厂。”

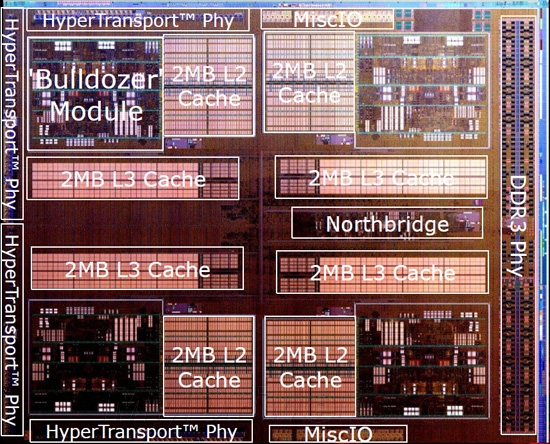

现在还不知道AMD是否用自动工具设计了整个推土机芯片,但看起来至少一些低效率的部分就是这么来的。按照AMD提供的数据,推土机芯片包含多达20亿个晶体管,是自家上代六核心以及Intel Sandy Bridge的两倍多,整个芯片面积315平方毫米,不得不说规模庞大。

细分起来,推土机的每个双核心模块再加2MB二级缓存用了2.13亿个晶体管,面积30.9平方毫米,四模块八核心就是8.52亿个晶体管、123.6平方毫米。8MB三级缓存(6bpc)的具体晶体管数量没有公开,估计约为4.05亿个。这样还剩下大约7.5亿个晶体管被用在了HT总线、I/O输入输出、内存控制器等模块以及其它杂七杂八的内部逻辑和路由之上,占用的芯片面积也着实不小,效率显然太低。

虽然无法确认,但可以猜测得出来,自动设计工具让推土机额外背负了多达几亿个晶体管的负担,后果就不言自明了。

顺便提一句,Intel Sandy Bridge的晶体管最多9.95亿个,核心面积258平方毫米,价格最高317美元,而推土机最多只卖245美元,期间的利润差距也就不用多说了。

最后需要提醒大家的是,上边的说法也只是某个人的一家之言,并不能反映所有的实际情况,而且也有读者回应说其实Intel也大部分都改用了自动设计,甚至有人说Cliff A. Maier提到的情况都是几年前的了,所以大家看看就是了,不比过于较真。