正文内容 评论(0)

按:上周,Intel在IDF开发者论坛上正式宣称“多核心(与现有桌面级CPU数量级不同)时代已经到来”,我们近期将会推出若干篇文章整理并解析这一宣言背后的深意,主要在高性能计算/超级计算机方向,本文来源于日本4gamers,主要资料为Intel数据中心负责人在新闻发布会上宣布的内容

8月底,Intel副总裁、Data Center(数据中心)部门负责人Kirk Skaugen在日本举行的该部门新闻发布会“面向ExaScale时代的Intel云战略:‘Cloud 2015’”上发表演讲,其中大部分内容是关于企业的云存储等内容。而我们主要关注的是其中Intel在2018年实现ExaScale计算的主要组成部分——MIC,即Many Intergrated Core多核心处理器,本文将整理并一一列举目前MIC与ExaScale的发展现状。

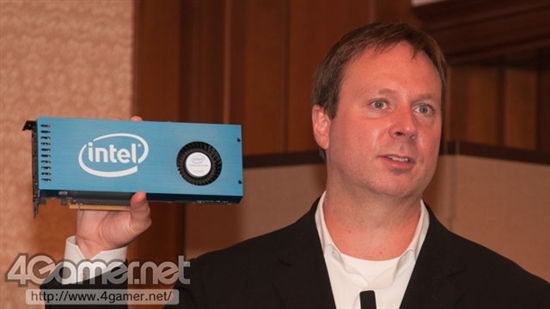

手持MIC早期测试用样品的Intel副总裁、Data Center部门主管Kirk Skaugen

MIC:超过1000名工程师参与研发的大计划

MIC(Many Intergrated Core)计划就如其名,是将多个(远超目前桌面CPU的核心数量)核心整合在一起的处理器,系列开发代号为"Knights",面向HPC(High Performance Computing)高性能计算领域。

现有的不少超级计算机,以及未来的HPC用处理器如我们之前介绍的NVIDIA Echelon等,均采用以CPU为主体,主力运算基于GPU的混合加速运算架构(Heterogeneous)。于此不同的是,Knights系列则属于采用和主CPU架构基本相同的多个x86核心集成来辅助主CPU运算的类型(Homogeneous)。现有样品代号为"Knights Ferry",集成45nm工艺制造的32个x86核心,连接界面采用PCI-Express x16,已分发给MIC计划的合作伙伴,供它们在此基础上进一步研究和开发。

目前Knights Ferry的合作伙伴,和NVIDIA的Echelon一样也是群英荟萃

不过Knights Ferry所集成的x86核心和Intel桌面CPU还不太一样,它采用的指令集和Intel在Sandy Bridge中引入的AVX类似,但进一步扩展到了512bit。记忆力好的读者可能还记得Intel之前夭折的GPU开发计划"Larrabee",Intel现在证实,MIC项目的主体就是对Larrabee计划作出修正和继承多数成果的Knights系列,说MIC计划是Larrabee的“转世重生”也不为过,但转世后的“心脏”却不一样了。

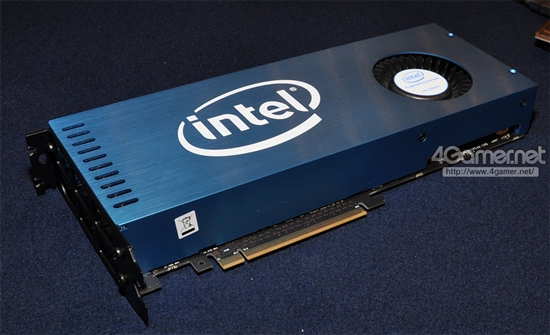

Knights Ferry加速卡的工程样品,延续Larrabee时代的设计,同时为PCI-E辅助供电接口预留了空位。Skaugen称下一个版本将会改变设计

关于MIC计划的进展,Skaugen称“开发一直在按照预定计划进行中。Intel将依靠此MIC架构实现在2018年HPC计算达到ExaScale的目标”。

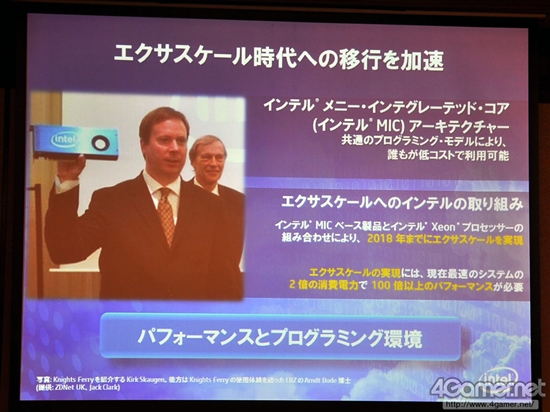

Intel揭示了以MIC架构处理器作为武器,在2018年实现ExaScale的目标

至于ExaScale,则是指拥有1Exa FLOPS(=1000Peta FLOPS,10的18次方)浮点运算能力的超级计算机。针对此目标,Intel在8月30日成立了子公司Intel Federal,专门与美国联邦政府机构协作研究高性能计算机。Skaugen称,子公司目前的主要使命是与美国政府携手达成ExaScale的目标,此外也不排斥而是欢迎其他国家参与合作。

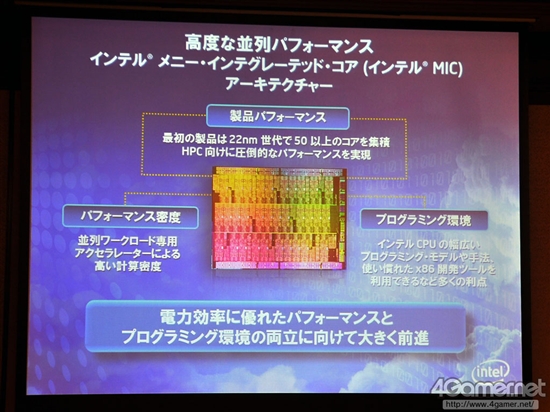

接下来就是走向ExaScale途中具体的产品路线图,Skaugen重申了Knights系列下一代产品将是采用22nm工艺制造,可在编程环境中同时利用50个x86核心的Knights Corner。他还透露作为通向ExaScale的重要一站,目前阶段的MIC计划有约1000人的Intel工程师参与研发,显示了Intel对于ExaScale目标的决心。

Knights Corner采用22nm工艺制造,将集成50个以上的x86核心,但具体数目是多少目前仍然未知

此次在日本举行的新闻发布会邀请的客座演讲嘉宾为东京大学石川裕博士,石川在东京大学的研究工作主要是是研究用MIC计划产品能组建怎样的HPC系统。

石川裕,东京大学研究生院情报理工学系计算机科学专业教授

石川自称选择MIC的主要理由是“单独的GPU无法运转”,没有主CPU的辅助GPU在通用计算中的作用也无从发挥,而集成多个x86核心的MIC就不一样(按:这也就是之前提到过的为什么NVIDIA要开发自家CPU Denver的原因)。此外作为单一CPU架构组成的MIC,另一个有利之处就是通用性要比GPGPU高。

石川研究组目前的主要课题是开发使用MIC的HPC用操作系统与应用软件。今后的研究方向将不仅限于发挥MIC的计算能力,也将注意提高I/O部分的性能。石川称:“HP的计算能力不仅仅用于单纯的科学计算,在细胞、结构生物学等需要解析大量数据的应用也能发挥作用,为此需要改善I/O性能。”石川研究组今后的目标是开发满足并行计算性能和I/O性能同时提高要求的硬件和软件。

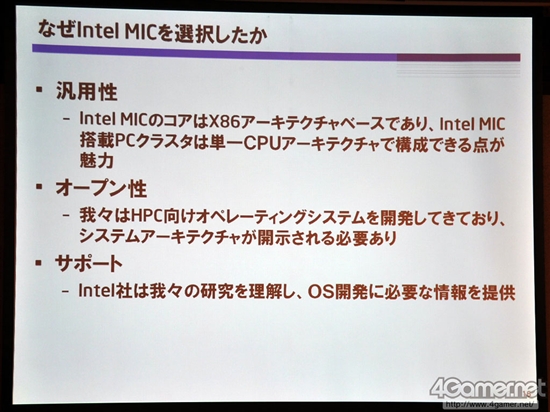

石川举例说明MIC架构的优点,包括通用性、开放性和Intel给予的研发支持

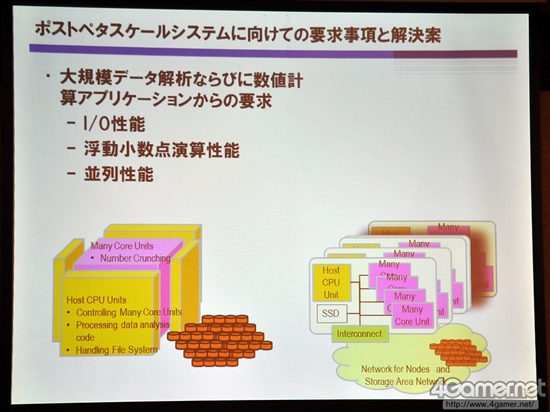

石川说明后Peta(即Exa)Scale级别系统的要求和解决方法,针对需进行大量数据解析的应用,需要着重于提高I/O性能、浮点运算性能和并行计算性能

石川研究组的另外一个针对ExaScale的课题就是故障。ExaScale级别的硬件肯定需要比之前更多的能源,而Skaugen和石川都提到目前工艺制造出的ExaScale级别超级计算机功耗完全超出范围,根本无法运行,所以改进工艺降低功耗是个很重要的课题。

集成大量CPU的ExaScale超级计算机的强大能力使得它如果遭到硬件故障宕机一日,后果不堪设想。石川研究的另一个课题就是在HPC遭遇硬件故障无法使用之前导出和备份运算数据。

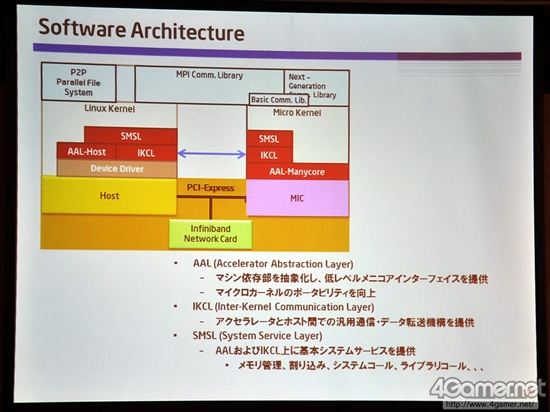

石川研究组开发的软件架构,HPC中主CPU运行Linux Kernel,MIC运行Micro Kernel,通过PCI-E界面连接并共用网络接口

小结

Intel已经在Knights系列产品和MIC架构上投入了巨额资金和研发力量,并且此技术目前还毫无进入消费级别市场的迹象。Larrabee计划也早已取消,未来Intel的集成GPU采用MIC技术的可能性也很低,可能只会达到共用指令集的程度。

Intel、NVIDIA相继在目标为ExaScale计算能力的道路上越走越远,此外还有IBM和Oracle在虎视眈眈,没有拿出HPC计划的主流芯片企业只剩AMD一家,相信在2018年为ExaScale设定的目标达成年到来前业界还会有一番龙争虎斗。