正文内容 评论(0)

VIA威盛近日邀请多名媒体记者前往位于美国德州奥斯汀的Centaur处理器研发总部,没有任何先兆地公布了自己的第一款四核心处理器“VIA QuadCore L4700”。下边我们一方面再深入了解这颗四核心,另一方面也看看VIA坚强的处理器研发部门究竟是个什么样子。

第一部分:VIA的四核心处理器

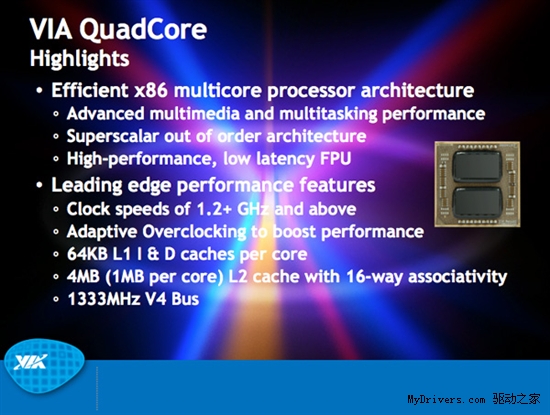

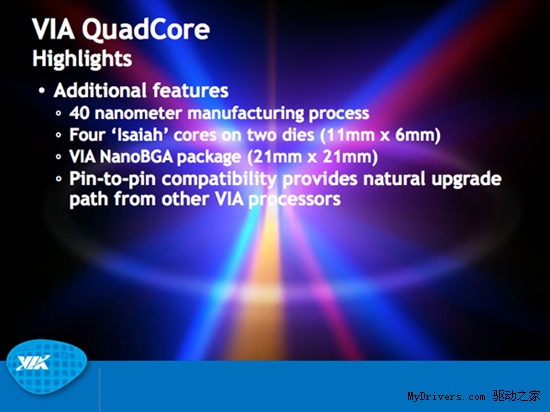

VIA QuadCore四核心在架构上不算很先进,依然沿用“Isaiah”,只是将两颗Nano X2双核心的内核(Die)放在一块基片上,然后通过一条1333MHz V4总线连接起来,类似Intel当年的早期双核心Pentium D、四核心Core 2 Quad。

制造工艺是台积电40nm,内核尺寸11×6毫米,整体封装尺寸21×21毫米,与其它任何VIA处理器都针脚兼容。

VIA QuadCore在架构上当然也是完全兼容64-bit x86,指令集最高支持SSE4。每个核心都是三发射乱序执行,性能上优于Intel Atom(双发射顺序执行)、AMD Bobcat(双发射乱序执行)。

处理器的每个核心都有64KB一级指令缓存和64KB一级数据缓存,每两个核心还有16路关联的2MB二级缓存,总计4MB。

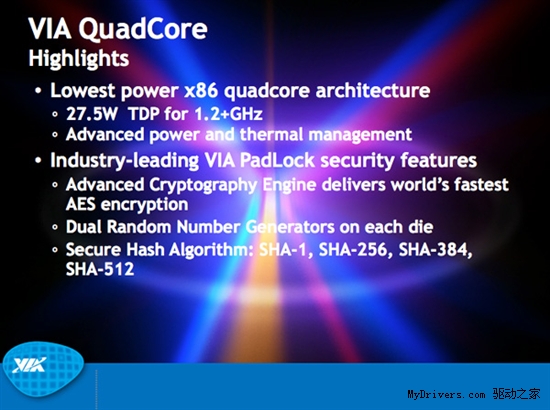

VIA QuadCore L4700的主频标注为1.2+GHz,通过自适应超频技术可以自动加速到最高1.47GHz,同时不超过27.5W的热设计功耗限制。这样的功耗其实不算低,加上芯片组的5W就是32W左右,已经两倍于AMD E-350 APU平台。VIA表示今后还会增加低频率、低功耗的节能版,但未透露更多细节。

值得一提的是,VIA QuadCore并不支持电源栅极控制,仅支持时钟栅极。

安全方面照例集成业界领先的PadLock安全技术,包括号称世界最快AES加密的高级密码引擎、每个内核上两个随机数生成器、SHA-1/SHA-256/SHA-384/SHA-512安全哈希算法等等。

VIA QuadCore四核心处理器面临的最大问题依然不是规格参数,而是市场生存空间,尤其是缺乏强大的OEM生态系统支持,目前只有一些白牌机和主板设计,却没有华硕、三星等大厂的支持。其实基于VIA QuadCore四核心处理器的系统如果定价合适,还是能够提供不错的体验的,就看有没有人愿意用它了。

第二部分:VIA的处理器研发部门

Centaur是在12年前被收归VIA旗下的,此后就成为VIA在海外的处理器研发总部。负责此次介绍与参观的Glenn Henry堪称元老级人物,从公司创建之初仅有四个人的时候一直忙活到现在。如今,Centaur已经有101名员工,比被收购的时候增加了30人。

Glenn Henry(背景是双核心Nano X2的内核图)

微处理器的设计并不是一拍脑门,想出个新架构,然后希望它能够高速运行。要想开发新处理器,你需要做大量的模拟。首先是软件模拟,并决定如何部署缓存容量、资源平衡甚至底层架构。后边需要在大型FPGA或者其它类似系统上进行硬件模拟,目的是进行功能性验证,而非性能验证。流片和制造是异常昂贵的(硅掩膜非常花钱),时间又很漫长(从流片到试产至少两个月)。

任何芯片设计企业都有大片的服务器集群,负责进行芯片设计的模拟和认证,Intel、AMD、NVIDIA、VIA莫不如此。

本文收录在

#快讯

- 热门文章

- 换一波

- 好物推荐

- 换一波

- 关注我们

-

微博:快科技官方

快科技官方微博 -

今日头条:快科技

带来硬件软件、手机数码最快资讯! -

抖音:kkjcn

科技快讯、手机开箱、产品体验、应用推荐...