正文内容 评论(0)

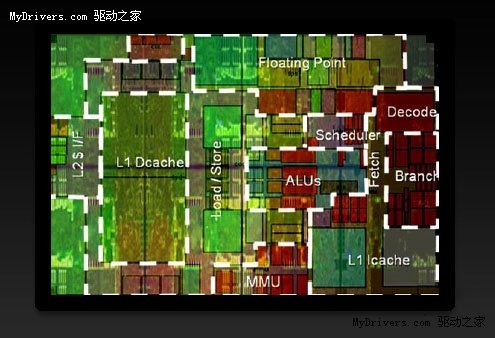

2011年财务分析师会议上,NVIDIA老大黄仁勋不仅谈到了ARM架构处理器“丹佛工程”(Project Denver)的一些幕后故事,还第一次曝光了这颗64位处理器的内核照片(或者说示意图):

这至少证明,NVIDIA已经获得了基本成型的丹佛处理器样品,也在自己的处理器之路上迈出了坚定的一步。当然了,由于一切还在发展之中,该处理器最后是个什么样子还很难说。就目前而言,制造工艺、内核面积等参数都无从得知,不过NVIDIA倒是很贴心地标识了各个功能模块的名称和范围,让我们对丹佛处理器的内部情况有了初步了解。

从图赏可以看出:

拾取单元

解码单元

调度器

算术逻辑单元(ALC)

浮点单元(FPU)

载入与存储单元

内存管理单元(MMU)

一级指令缓存(L1 Icache)

一级数据缓存(L1 Dcache)

二级缓存逻辑指令与拾取单元

面积最大的当属一级数据缓存,另外一级数据缓存、浮点单元也都不小。如果代号麦克斯韦(Maxwell)的NVIDIA下一代GPU处理器使用512-bit位宽和高速GDDR5颗粒,其内置的丹佛处理器核心有望获得2TB/s以上的内部带宽和320GB/s以上的外部带宽。那可是一颗重磅炸弹。

当然了,丹佛工程能否成功,不仅仅在于NVIDIA要制造出一颗真正完善的处理器芯片,更关键的是NVIDIA能否建立一套完整的生态系统。

本文收录在

#快讯

- 热门文章

- 换一波

- 好物推荐

- 换一波

- 关注我们

-

微博:快科技官方

快科技官方微博 -

今日头条:快科技

带来硬件软件、手机数码最快资讯! -

抖音:kkjcn

科技快讯、手机开箱、产品体验、应用推荐...