正文内容 评论(0)

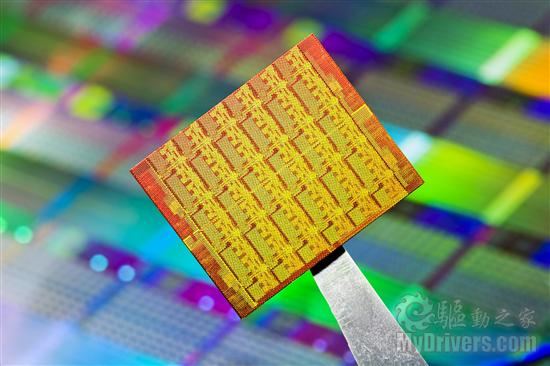

2009年底,Intel展示了48核心单芯片云计算机(SCC),全球第一款拥有48个x86处理核心的处理器芯片。仅仅半年之后,Intel就向软件开发商出货了基于这种处理器的试验系统,但同时表示它只是一个研究项目,并不会投入商用。尽管如此,48核心处理器早已获得了业界的广泛关注,因为它既代表着微处理器发展的一个未来方向,也隐约之中有可能传递Larrabee项目的香火。

X-bit Labs近日专访了Intel德国不伦瑞克研究院主管、48核心处理器的两位设计主管之一Sebastian Steibl。Intel欧洲研究院是一个相当庞大的组织,旗下有包括不伦瑞克在内的20个实验室,拥有大约900名研究员。

问:有消息称SCC拥有48个 P54C核心,也就是奔腾内核。消息是否准确?或者说SCC的内核更加先进、堪比Larrabee图形处理器?

答:我们把它们叫作奔腾级别核心(Pentium-class cores)。它们的特征是“拥有顺序短管线的小核心”,本质上和P54C相同,和奔腾具有相当程度的可比性。

问:为什么决定使用这些非常古老的核心?

答:SCC的主要目标是创建一个研究平台,在特定大小的芯片上集成尽可能多的核心,为此不得不牺牲单个核心的性能和面积,否则不可能装入这么多核心。我们发现,奔腾级别核心的编程工具支持极佳,直到现在所有的编程工具都支持它。如果使用更小的核心(以及更先进的微架构),来自标准编译器的支持就会受到限制。总之,奔腾级别核心拥有世界级编程工具的支持,完全兼容IA架构,面积很小,所以我们选择了它。

问:SCC的晶体管数量是多少?

答:大约13亿个。

问:SCC的设计浮点性能有多高?

答:实际性能并不是SCC的设计目标。奔腾核心没有矢量浮点单元,因此浮点性能不会很高。我们的目标是提高芯片的并行处理能力,而不是浮点性能的最大化。如果加入矢量浮点单元,就得占据更多核心面积,更重要的是功耗也会增加。既然我们想要的是尽可能高的并行能力来研究高级多核心软件,我们决定不去盲目追求浮点性能。

问:您认为未来的多核心处理器是像今天这样拥有大量简单核心而高级核心数量有限,还是或许尽量拥有更多的高级核心?

答:作为一名研究人员,我不能代表产品事业部发表评论,只能谈论我们眼中的趋势。如果你看看今天的软件,即使是多核心软件,很多时候都需要(尽可能高的)单线程性能,不过也有应用能从多线程性能中获益。

对于今后的处理器,单线程性能在可预见的未来内仍然很重要。软件产业也需要能够充分利用并行处理机制的工具,这也是我们向感兴趣的学术机构分发SCC的原因之一,以便供他们研究多核心编程的高级方法、提高效率。

在可预见的未来内,大核心仍然会扮演重要的角色。

问:对于高端处理器来说,增加新的指令集、特殊目的加速器、类似GPU内部的算术逻辑单元、宽范围矢量处理单元,哪个更重要?

答:我想它们都差不多。在高性能处理中,我们需要矢量单元。这个我们一直在增加,而且取得了不错的效果。在移动领域,加速器扮演着重要角色,因为移动计算的地位正在越来越高。我想未来它们都会继续存在。事实上,我们在这两个方向上都有研究项目。

问:带有WLIW(超长指令字)矢量单元之类加速器的x86架构能够更快地处理图形么?

答:绝对能!Intel新的Sandy Bridge、AMD新的Llano及其小兄弟Ontario都会这么做。我们会在2011年提供优秀的硬件,但是能够充分利用它的软件可能要等到2012或者2013年。

问:Intel为什么会让软件来决定处理器使用的核心数量?使用类似GPU内部的超线程(Ultra-Threaded)分配处理器是不是会在软件效率和复杂性上更有效率?

答:SCC是一个研究平台,我们尽力使之成为一个试验平台。在这种架构里,我们拥有数据流、执行管理。对开发平台来说,拥有这种能力要比固顶功能单元好得多。固定功能的数据调度器或许更高效,但是SCC这个项目让我们在软件组织方面更有弹性。

问:多核心处理器在未来是否能够同时处理通用数据和图形?(换言之CPU能否取代GPU)

答:如果图形操作能够简化成曲面细分之类的几何功能,以及着色器之类的图形功能,再加上不需要纹理单元、视频模块、颜色查找表之类的特殊处理器,那么答案绝对是肯定的。更进一步地,我想这一切会在五年之内发生,最短甚至只需要三年。需要特殊处理器的原因是缩短标量处理器的处理时间。有了多核心处理器和高频率,我们就能从容应付软件负载,让通用目的处理器运行高度特制应用。

问:SCC的核心之间并没有硬件二级缓存一致性,这么做是为了降低网格网络之间的带宽需求,还是Intel认为未来的多核心处理器不要二级缓存一致性?

答:这个其实取决于实际应用和数据局部性。不过我想,去掉缓存一致性简化了芯片设计,并降低了网格网络的功耗。

问:这么说未来的应用并非完全不需要缓存一致性?

答:关键在于对当前的并行计算机来说,在现有形式下是否需要缓存一致性。当前的所有架构其实都是缓存关联的,所以我们特意设计了一个非缓存一致性架构,看看这么做能走多远,而缓存一致性可以在软件内管理。我们这么做是因为超级计算机通常都不是一致性的,如果你在高性能计算中有几千个计算节点就不是。所以,我们知道确实存在没有一致性的伸缩编程模型。现有的片上编程模型是完全一致性的,所以我们想看看非一致性模型是否能在大量核心上实现,在50、100甚至更多节点上没有硬件一致性是否会成为并行软件的瓶颈。

问:SCC中每两个核心组成的Tile可以运行在自己的频率上,内存控制器也有不同的频率,但整个网格网络看起来却是统一频率。未来芯片是否也会这样不同的部分有着不同的内部频率?

答:我不是产品事业部的,所以不能对实际产品发表评论,但是我们创造了这种试验芯片,所以如果微处理器永远停留在同样的时钟频率上,我肯定会很吃惊。作为研究人员,我个人同意你的说法。当然停留在同样的频率上也有好处,比如说控制功率门限。除了频率不同之外也有其他选择,比如降低芯片某些部分的速度,甚至在特定始终循环里彻底关闭某一部分。我想我们会看到芯片的不同部分根据任务需要运行在不同性能点上。

问:AMD Llano之类的异构多核心理念是不是会更好一些?

答:异构处理是最理想的方案,但也有一些需要注意的地方,比如应用负载均衡、标量处理,矢量处理也是很复杂、低效的。只有在应用程序内通过指令集才能实现。如果操作系统或者常驻内核能够分析应用程序的需要,将负载导向何时的处理器(矢量、标量、矩阵等等),集成异构处理器的效率将是惊人的。

硬件正在拉大相对于软件的领先地位。二十世纪八十年代,硬件的效率无法满足软件;九十年代初,硬件和软件基本持平;新千年里,硬件能力每隔一年就能超过软件需要大约六个月。软件开发还没有自己的摩尔定律。

问:您如何看待AMD Fusion理念?它是否会成功?

答:它不仅会成功,也是不必避免、必不可少的。它对物理分离的标量和矢量处理器来说效率不足(综合起来就高效了)。通过三级缓存进行处理器内部通信的优势非常明显,不容忽视。还有新的制造工艺。打造这种超级复杂的系统是经济可行的。

问:你们是如何将48个核心放在一起并保持125W热设计功耗的?这太牛了。

答:我们有能力很好地管理功耗,比如不同的电压和频率分区,同时我们也在设计方面做出了一些牺牲(比如前边提到的缺乏矢量浮点单元和二级缓存一致性)。

问:关于SCC集成的高效四通道DDR3内存控制器有没有更多信息可以透露?它和目前使用的内存控制器有何不同?

答:SCC里的内存控制器是根据不同操作点进行优化的。每个内存控制器需要配合12个核心,就并行机制而言是相当多的,因此它针对更好地管理大量单线程进行了优化,而不是少量多线程。它针对更高并行度的访问进行了优化,而传统内存控制器更适合有限数量线程情况下的性能。

问:那么这代表着内存控制器的未来?

答:它是一种适合多核心架构的内存控制器,也能很好地用于大核心。

问:在SCC项目上,软件开发产业有什么责任?这种系统是否已向软件厂商出货?

答:我们已经开始和特定的外部合作伙伴分享这种系统。目前已经取得了一些很有趣的成果,而且我想今年夏天还会有更有趣的消息。这些机构才应该对他们的成果发表评论。