正文内容 评论(0)

旧金山秋季IDF 2009开幕在即,Intel不但公布了详细的日程安排,还提前放出了不少技术资料,介绍了本次峰会的两大主题:32nm半导体工艺、基于Nehalem架构的低功耗嵌入式Xeon处理器。

32nm工艺将用于2010年的Core Westmere家族处理器和未来的SoC片上系统处理器,均使用了第二代高K金属栅极(HK+MG)晶体管技术,特别后者是Intel第一次开发的全功能SoC制造工艺,特殊特性包括高压I/O晶体管、二代HK+MG超低功耗晶体管等等,还有新的高精度、高质量的电阻、电容、电感等无源元件,专为SoC设备需要而设计。

Intel的HK+MG晶体管首次应用45nm工艺,相关处理器的出货量从2007年11月以来累计超过2亿颗。新一代32nm工艺则定于今年第四季度投产并获得收入,首批产品是明年年初的双核心Clarkdale系列。

Intel声称,按照驱动电流计算的话,其32nm工艺是当今业界所有32/28nm工艺中性能最高的,PMOS管和NMOS管的性能相比45nm时代分别提升了19%和28%,同时密度也是最高的,晶体管栅极间距(Transistor Gate Pitch)仅为112.5nm——此值越小意味着单位面积内能够集成的晶体管数量越多,可以带来更多功能、更高性能。

参考:【Intel 32nm工艺专题:70亿美元铸就新辉煌】

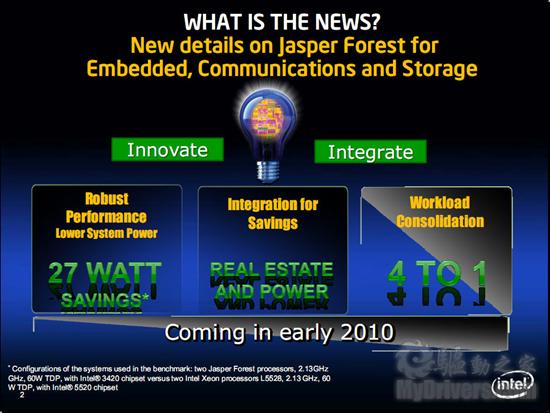

下边再看看代号“Jasper Forest”、专为嵌入式通讯与存储应用设计的新一代Xeon处理器。

这种处理器同样基于45nm Nehalem微架构,采用双芯片设计并首次集成了PCI-E I/O,每颗芯片使用16条PCI-E 2.0 x16通道,并搭配Intel 3420芯片组,而且功耗相比常规型的Xeon 5500、5520+ICH10R的组合降低了27W。

Jasper Forest的扩展性非常强,既有23-30W的单核心,也有35-65W的双核心,更有48-85W的四核心,而且插槽通用。

其它技术特性:

- 非透明桥接(NTB):支持多个系统通过一个PCI-E链接进行无缝连接,无需再使用外部PCI-E交换。

- 集成RAID硬件加速:支持存储客户迁移到Intel平台或转换RAID以用于核心优化。

- 集成异步ADRAM自刷新内存:可在电源出现故障时保护重要数据。

- Crystal Beach DMA

Intel表示,Jasper Forest将于2010年初发布,生命周期支持七年,可靠性更是长达十年,非常适合IPTV、VoIP、NAS、SAN和无线电网络控制器等密集型存储和通讯解决方案,可用于通信、存储、无线基础设施、路由器、军事和安全等诸多领域。