正文内容 评论(0)

斯坦福大学举办的年度处理器会议Hot Chip 21正在进行之中,AMD、Intel、IBM、Sun四大巨头全部到场,分别准备了12核心Opteron、八核心Nehalem-EX(Xeon 7500)、Power 7和代号Rainbow Falls的第三代Sparc Niagara。之前已经预告了IBM Power 7,这里再首先初步看一下AMD的首款12核心处理器,其他更多资料稍后。

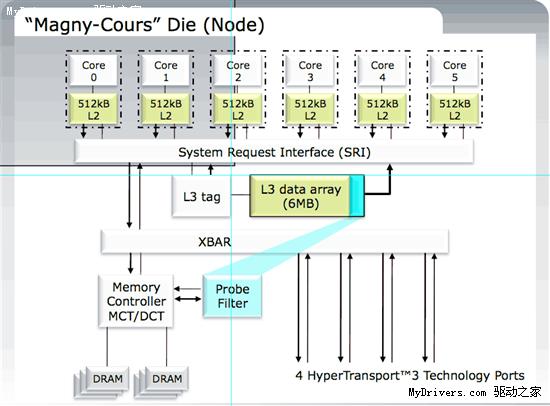

AMD的这颗处理器代号为“马尼库尔”(Magny-Cours),由两颗六核心伊斯坦布尔封装在一起而成,和Intel惯常采用的多核心设计方式如出一辙,都是多芯片模块(MCM)。

随着处理器核心数的增多,原生设计的难度急剧增大,所以AMD今后也会改变思路,通过多DIE封装的形式向更多核心过渡。AMD资深技术骨干Pat Conway表示:“基本上我们参考了(Intel的)教科书,但做法不同。”

在马尼库尔的每一个DIE中,都有六个处理器核心和各自相应的512KB二级缓存,彼此之间通过系统请求界面(SRI)进行通信,同时共享6MB三级缓存,再通过切换控制器(XBAR)连接双通道DDR3内存控制器和四条HT 3.0总线。这样一来,双路系统中的数据只需一次传输即可达到任何一颗核心,四路系统中则需要两次。

相比之下,Intel之前的双DIE封装多核心处理器都要集体通过前端总线(FSB)去连接北桥芯片里的内存控制器,而集成了内存控制器的Nehalem架构现在还都是原生多核心。

AMD也同时改变了内存协议,不再向所有核心广播缓存一致性检查,而是从三级缓存里单独分出1MB的空间来保存一个表格,跟踪所有缓存数据,能将服务器的内存延迟从120纳秒降低到50纳秒,大大提高性能。这其实也就是之前在介绍六核心伊斯坦布尔时屡屡提到的探测过滤器技术“HT Assist”,它将在AMD未来所有的服务器处理器中使用,可通过BIOS开启或关闭。

Pat Conway指出:“三级缓存从6MB减少到5MB的负面影响很小,而从系统层面上看能够降低内存延迟、提高系统带宽,显然是非常明智之举。”

他还确认马尼库尔将在2010年第一季度如期发布,命名为新的Opteron 6000系列,接口也会换成1974个针脚的Socket G34,频率上据AMD透露会比六核心伊斯坦布尔低25%左右,因为要在核心数量翻番的情况下保证功耗水平。

在服务器领域,AMD的下一次重拳出击将是业界期待已久的“推土机”(Bulldozer)架构。新架构的具体资料基本没有,但也会采用马尼库尔似的MCM设计方式,并会改变AMD长期以来的单线程属性,用Pat Conway的话说就是带来一种“不同于超线程(Intel HT)的新风格”,因为后者只是单核心双线程——难道AMD要单核心多线程?

本文收录在

#快讯

- 热门文章

- 换一波

- 好物推荐

- 换一波

- 关注我们

-

微博:快科技官方

快科技官方微博 -

今日头条:快科技

带来硬件软件、手机数码最快资讯! -

抖音:kkjcn

科技快讯、手机开箱、产品体验、应用推荐...